发布时间:2025-08-27 阅读量:50 来源: 发布人: bebop

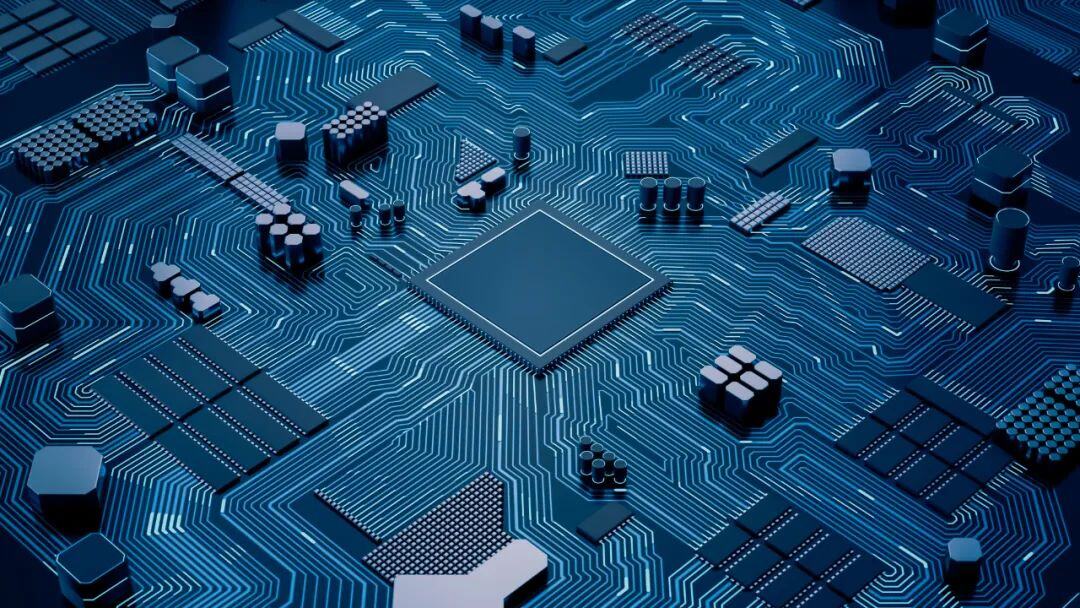

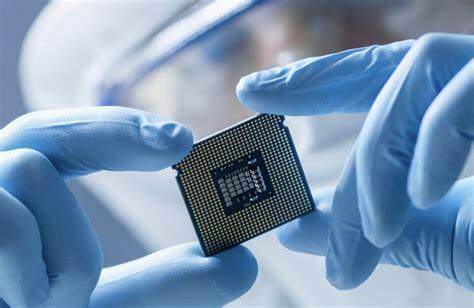

在当今高度集成的半导体世界中,每一枚微小的芯片都凝聚着尖端科技的结晶。从智能手机到超级计算机,从自动驾驶汽车到人工智能系统,芯片的性能与可靠性直接决定了电子设备的上限。而在芯片设计与制造的复杂流程中,有一个常被忽视却至关重要的结构——Seal Ring(密封环)。它虽不参与核心逻辑运算,却如同芯片的“隐形守护者”,默默保障着芯片的稳定与安全。那么,Seal Ring 技术究竟是什么?它为何如此重要?本文将为您揭开这一关键技术的神秘面纱。

Seal Ring,中文常译为“密封环”或“保护环”,是位于芯片最外层的一圈特殊结构,通常由多层金属和介质材料构成,环绕在芯片有源电路区域(即核心功能模块)的四周。它并非用于信号传输或数据处理,而是作为一种物理和电气的“防护屏障”,主要作用是保护芯片内部精密的电路结构免受外部环境和制造工艺的影响。

Seal Ring 的设计通常遵循严格的工艺规则,其宽度、层数和材料选择需与芯片的制程节点、封装方式以及应用场景相匹配。在现代先进制程(如7nm、5nm甚至3nm)中,Seal Ring 的设计更是成为确保芯片良率和可靠性的关键环节。

防止湿气与污染物侵入

在芯片封装和使用过程中,湿气、灰尘或其他化学污染物可能通过芯片边缘渗透进入内部,导致金属线路腐蚀或短路。Seal Ring 通过形成致密的物理屏障,有效阻隔这些有害物质的侵入,延长芯片寿命。

提升机械强度与抗应力能力

芯片在切割(dicing)、封装和后续使用中会受到机械应力,边缘区域尤为脆弱。Seal Ring 增强了芯片边缘的结构强度,减少因应力集中导致的裂纹或分层现象,从而提高芯片的机械可靠性。

抑制晶圆切割损伤(Dicing Damage)

在晶圆被切割成单个芯片的过程中,切割工具可能对边缘电路造成微小损伤。Seal Ring 位于切割线(scribe line)附近,能够吸收部分切割能量,保护内部电路不受影响。

静电放电(ESD)防护

某些 Seal Ring 设计还集成了静电放电保护结构,帮助泄放芯片在制造、运输或使用过程中积累的静电,避免敏感电路被击穿。

改善化学机械抛光(CMP)均匀性

在芯片制造的化学机械抛光步骤中,不同区域的材料去除速率可能不一致,导致表面不平整。Seal Ring 有助于平衡芯片边缘与中心区域的材料分布,提升抛光均匀性,从而保证后续工艺的精度。

随着芯片制程不断微缩,Seal Ring 的设计面临更高要求。在纳米级工艺中,电路密度极高,留给 Seal Ring 的空间被极度压缩。如何在有限面积内实现多重防护功能,同时不影响芯片整体尺寸和成本,成为设计工程师的一大挑战。此外,3D封装、Chiplet(芯粒)等新技术的兴起,也对 Seal Ring 的兼容性和集成能力提出了新要求。

尽管 Seal Ring 不直接参与芯片的功能实现,但它却是确保芯片高良率、高可靠性和长寿命的“幕后英雄”。从防止物理损伤到抵御环境侵蚀,从提升制造良率到增强产品稳定性,Seal Ring 技术在半导体产业链中扮演着不可或缺的角色。未来,随着芯片向更小尺寸、更高集成度发展,Seal Ring 的设计将更加智能化与多功能化,继续为“中国芯”的崛起保驾护航。

了解 Seal Ring,不仅是理解芯片制造的关键一环,更是洞悉现代电子科技底层逻辑的重要窗口。

近日,AI芯片企业寒武纪(Cambricon)发布业绩预告,其营收或利润出现惊人增长,同比增幅高达4300%,引发资本市场和科技行业的广泛关注。这一数据不仅标志着寒武纪自身发展的重大突破,也折射出中国AI芯片行业在技术突破、市场拓展和生态构建方面的显著进展。

BLDC电机控制与驱动器技术正朝着智能化、集成化、高效化方向持续演进。

霍尔效应是指当电流垂直于外磁场方向通过导体时,在导体两侧会产生电势差的现象。在现代材料科学和半导体工业中,霍尔效应测试已成为表征材料电学性能的重要手段,能够精确测量载流子浓度、迁移率、电阻率等关键参数。然而,精确的霍尔测量面临着多重技术挑战:微弱信号的检测(通常为微伏级)、高精度电流源需求、复杂的温度环境影响以及多参数同步测量需求。

14名犯罪嫌疑人因非法获取、泄露华为公司商业秘密,被法院依法判处有期徒刑。

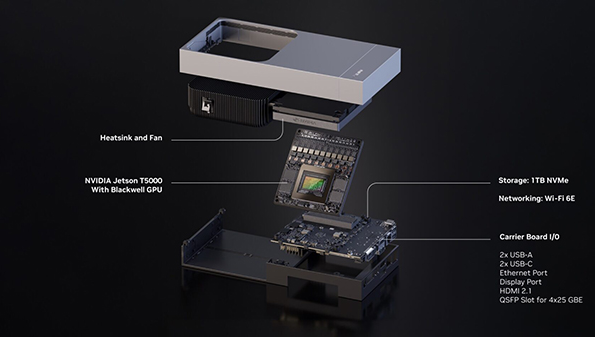

全球人工智能与机器人领域迎来又一里程碑事件,芯片巨头英伟达(NVIDIA)正式发布了其新一代机器人计算平台——Jetson Thor系列。该芯片并非此前Jetson Orin系列的简单迭代,而是基于NVIDIA Thor SoC(系统级芯片)打造,专为性能密集型仿人机器人和自主机器设计,被业界誉为“迄今性能最强的机器人专用芯片”。它的发布,标志着具身智能(Embodied AI)向大规模、复杂化应用迈出了关键一步。