发布时间:2025-08-21 阅读量:72 来源: 发布人: suii

在现代电子设备中,USB接口已成为数据传输和电力供应的标准配置。一个优秀的USB接口PCB设计不仅能确保信号完整性,还能最大限度地发挥接口的理论传输速度。

USB接口的PCB设计涉及信号完整性、电源管理、电磁兼容性等多个方面,这些因素共同决定了最终产品的稳定性和性能表现。USB2.0采用半双工通信机制,理论传输速率480Mbps(实际有效吞吐约280Mbps),而USB3.0通过引入全双工架构和新增高速通道,实现了5Gbps(即USB3.0 Gen1)的理论带宽,实际有效吞吐可达3.2Gbps,实现了近10倍的性能跃升。

USB2.0与USB3.0的核心差异

USB2.0 和 USB3.0 在传输性能上有着明显差距:USB2.0 传输速率高达 480Mbps,而 USB3.0 的最大传输带宽能达到 5Gbps,并且引入了全双工数据传输模式。

想要搞懂它们的 PCB 设计,先得认识它们的 “身份标识”—— 管脚定义。

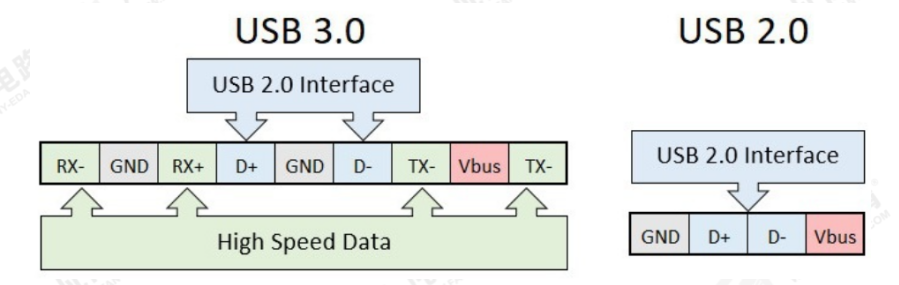

USB 2.0与USB 3.0管脚定义

从图中能清晰看到,USB3.0 相比 USB2.0,多了 RX-、RX+、TX-、TX + 等高速数据传输相关的管脚,这也是它能实现高速传输的重要基础。

二、USB 2.0接口的PCB设计要点

USB 2.0作为曾经的主流标准,其PCB设计相对简单,但仍有一些关键点需要注意:

1.差分对布线:USB 2.0使用一对差分信号线(D+和D-)进行数据传输。

2.阻抗控制:USB 2.0差分对的特性阻抗应控制在90Ω±10%。

3.缩短走线长度:USB 2.0信号线应尽可能短,一般不超过15cm,过长的走线会导致信号衰减和完整性下降。

4.避免锐角转弯:布线时应使用45°或圆弧转弯,避免90°直角转弯,以减少信号反射。

5.接地处理:在差分对下方提供完整的地平面,避免跨分割,确保良好的信号回流路径。

三、USB 3.x/Type-C的PCB设计进阶

随着USB 3.0及后续版本的推出,数据传输速率大幅提升,PCB设计的要求也更加严格:

1.多组差分对管理:USB 3.x引入了额外的两组差分对(TX和RX),Type-C更是支持多通道配置。每组差分对都需要严格匹配长度,通常长度差控制在2mil以内。

2.更严格的阻抗控制:USB 3.x差分对的特性阻抗要求为85Ω±5%,比USB 2.0更加精确。

3.层叠设计优化:高速USB信号建议布置在内层,上下都有完整的地平面提供屏蔽。外层走线容易受到干扰。

4.过孔优化:尽量减少过孔数量,必要时使用背钻技术去除过孔残桩,减少信号反射。

5.串扰控制:不同组差分对之间应保持足够间距(至少3倍线宽),必要时添加地线隔离。

USB接口的PCB设计是一门结合理论与实践的复杂技术,从USB 2.0到Type-C,设计难度和要求不断提升。需要在理解USB协议的基础上,掌握高速PCB设计技巧,结合实际情况做出合理权衡。只有注重每一个设计细节,才能充分发挥USB接口的性能潜力,为用户提供稳定可靠的高速数据传输体验.

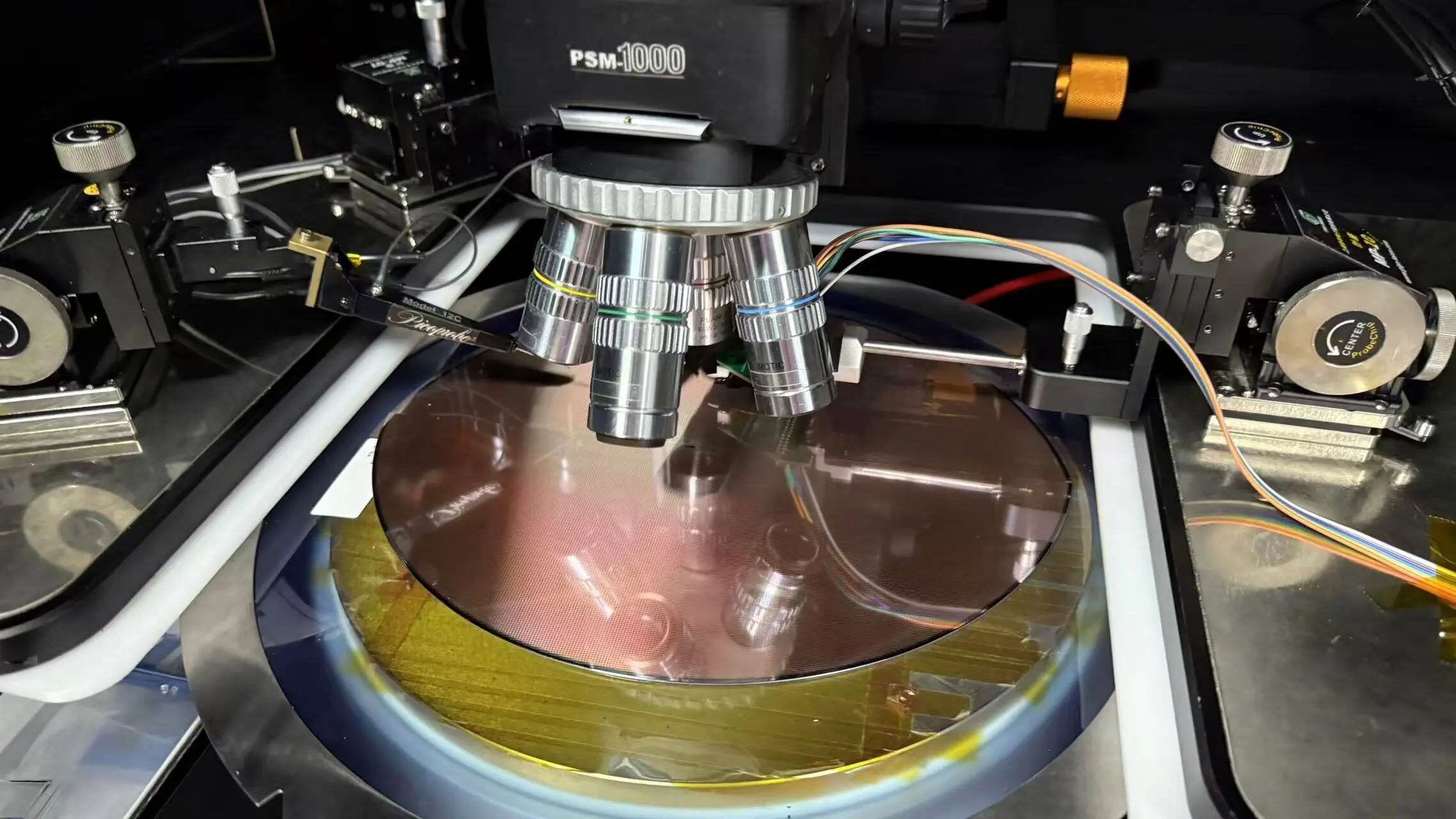

8月21日,中国半导体行业迎来里程碑式进展——领开半导体成功研发并量产28nm以下嵌入式闪存(e-Flash)技术,一举打破国外厂商在该领域的长期垄断。这一突破不仅填补了国内高端存储芯片的技术空白,更为国产MCU、汽车电子及AIoT设备的自主可控提供了关键支撑。

近日,有外媒报道称,美国特朗普政府正考虑以“国家安全”为由,强行入股包括英特尔在内的三大芯片巨头,以加强对半导体产业的控制。这一消息迅速引发行业震动,外界担忧此举可能重塑全球芯片产业格局,并对供应链产生深远影响。

在全球科技竞争格局深刻重构的背景下,中国电子产业正迎来国产替代与自主创新的历史性机遇。第106届中国电子展紧扣《"十四五"规划》制造强国战略,聚焦基础电子元器件、集成电路等"卡脖子"领域,集中展示从材料、设备到应用的国产化突破成果。

在现代电子系统设计中,混合信号PCB的接地策略直接影响电路性能与信号完整性。晶振作为时序控制的核心元件,其接地方式需严格遵循噪声抑制与电流回流路径优化的基本原则。

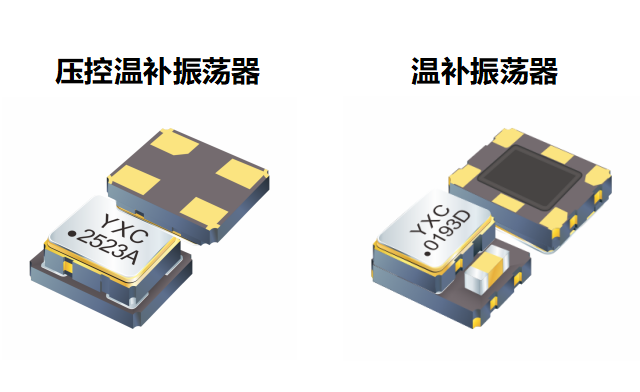

在精密电子系统中,时钟源的稳定性与精度直接影响整体性能。温补晶振(TCXO)凭借其优异的温度补偿特性,长期以来广泛应用于通信、导航等领域。然而,随着现代电子设备对频率控制要求的日益提高,压控温补晶振(VC-TCXO)因其兼具温度补偿与电压调谐能力,逐渐成为高精度场景下的潜在替代方案。