发布时间:2025-08-20 阅读量:46 来源: 发布人: suii

在现代电子系统设计中,混合信号PCB的接地策略直接影响电路性能与信号完整性。晶振作为时序控制的核心元件,其接地方式需严格遵循噪声抑制与电流回流路径优化的基本原则。

数字地、模拟地互相会影响不是因为一个叫数字,一个叫模拟,而是用了同一部电梯:地,而这部电梯所用的井道就是在PCB上布得地线。印制电路板(PCB)是电子产品中电路元件和器件的支撑件,它提供电路元件和器件之间的电气连接。现在有许多PCB 不再是单一功能电路,而是由数字电路和模拟电路混合构成的。数据一般在模拟电路中采集和接收,而带宽、增益用软件实现控制则必须数字化,所以在一块板上经常同时存在数字电路和模拟电路,甚至共享相同的元件。

那么晶振在电路中是接数字地还是模拟地?晶振以接数字地为主,具体有以下几种情形:

1、大多数数字系统:接数字地,确保低噪声电源和紧凑布局;

2、混合信号系统:接数字地,单点连接模拟地,重点关注回流路径;

3、高频/精密模拟:评估噪声敏感性,可能需接模拟地或隔离处理。

在电路设计中,晶振的接地处理需根据具体应用和系统架构决定。以下是关键考虑因素和建议:

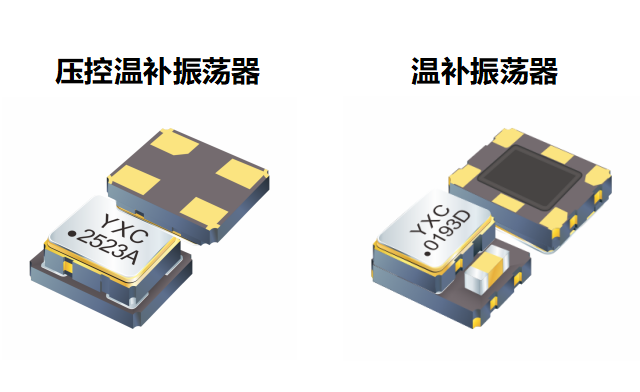

1、 晶振类型决定接地方式

无源晶振(需外部电路),通常建议接数字地,因为其驱动电路(如MCU的振荡器)属于数字范畴。高频噪声可能通过地平面耦合,需确保数字地干净;有源晶振(自带振荡电路),若为数字系统提供时钟,接数字地;若用于模拟电路(如射频、ADC),需评估是否接模拟地或通过磁珠/电容隔离。

2、 混合信号系统的处理

若系统同时存在数字地和模拟地,晶振(尤其是高速晶振)应接数字地,并在电源入口处通过0Ω电阻或磁珠将数字地与模拟地单点连接,避免地环路噪声。

高频晶振(如>10MHz)的回流路径需完整,地平面分割可能导致阻抗不连续,反而增加辐射。此时可优先保持完整地平面,通过布局隔离而非分割。

3、 降低噪声的关键措施

局部去耦,在晶振电源引脚就近放置0.1μF+10pF电容组合,形成低阻抗回路,高频噪声直接回流到地而非耦合到其他部分;晶振走线尽量短,且下方保持完整地平面,避免跨分割区。时钟信号远离模拟敏感线路;对高频或敏感电路,可用金属屏蔽罩覆盖晶振并接地,进一步抑制辐射。

4、 特殊场景建议

高频/射频系统若晶振用于射频本振,需严格接模拟地,并采用独立电源滤波,避免相位噪声恶化。

多时钟系统,不同晶振的地可通过局部星型连接汇聚到主接地点,减少相互干扰。

综上所述,随着电子系统向更高频率、更高集成度发展,晶振接地技术也面临新挑战。在PCB设计中,晶振的接地策略需综合考虑电路类型、工作频率及系统噪声敏感性。数字系统通常优先接数字地,而混合信号系统则需优化回流路径,避免地环路干扰。

在精密电子系统中,时钟源的稳定性与精度直接影响整体性能。温补晶振(TCXO)凭借其优异的温度补偿特性,长期以来广泛应用于通信、导航等领域。然而,随着现代电子设备对频率控制要求的日益提高,压控温补晶振(VC-TCXO)因其兼具温度补偿与电压调谐能力,逐渐成为高精度场景下的潜在替代方案。

据最新消息,苹果公司计划于2027年推出其首款机器人产品,这款代号为"Eve"的虚拟伴侣机器人,将结合苹果在硬件设计、人工智能和用户体验方面的优势,开创消费级机器人新品类。不同于传统功能性机器人,苹果的这款产品更注重情感连接和个性化陪伴,有望重新定义人机交互的未来。

在当前全球电子制造业向智能化、绿色化加速转型的背景下,产业链协同创新已成为突破技术壁垒的关键路径。本次走访聚焦微焦点X-RAY检测、自动化测试烧录一体化、半导体封装工艺等核心技术领域,通过构建"技术攻关-场景验证-生态协同"的三维合作模型,旨在打通从实验创新到规模化应用的最后一公里。

美国为防止高端人工智能(AI)芯片通过第三方渠道流入中国,已秘密要求芯片制造商英伟达(NVIDIA)、超威半导体(AMD)等企业在出口至部分国家的AI芯片中植入追踪程序,以便实时监控芯片流向

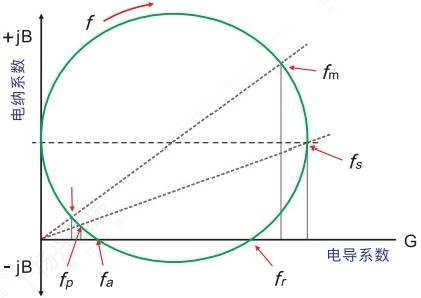

在电子电路设计中,晶振的每一项参数都与产品命运息息相关——哪怕只差0.1ppm,也可能让整板“翻车”。看似最基础的术语,正是硬件工程师每天必须跨越的隐形门槛。