发布时间:2025-06-16 阅读量:1584 来源: 安森美 发布人: wenwei

【导读】安森美(onsemi)推出的碳化硅共源共栅场效应晶体管(Cascode FET),通过创新架构融合SiC JFET与低压硅MOSFET,成功解决了SiC JFET常开特性的应用瓶颈。该设计兼具SiC材料的高效优势与硅器件的易控特性,在硬开关与软开关场景中展现显著性能提升。本文将深入剖析其结构原理及核心优势。

Cascode简介

碳化硅结型场效应晶体管(SiC JFET)相比其他竞争技术具有一些显著的优势,特别是在给定芯片面积下的低导通电阻(称为RDS.A)。为了实现最低的RDS.A,需要权衡的一点是其常开特性,这意味着如果没有栅源电压,或者JFET的栅极处于悬空状态,那么JFET将完全导通。

然而,开关模式在应用中通常需要常关状态。因此,将SiC JFET与低电压硅MOSFET以cascode 配置结合在一起,构造出一个常关开关模式“FET”,这种结构保留了大部分SiC JFET的优点。

Cascode结构

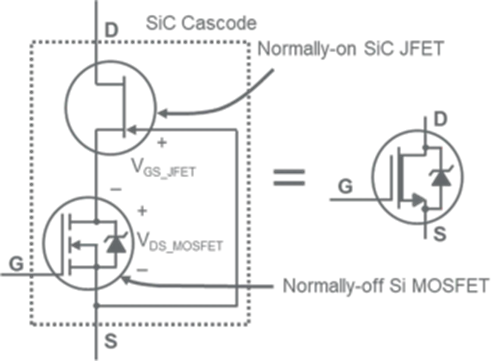

共源共栅(Cascode)结构是通过将一个SiC JFET与一个低压、常关的硅(Si)MOSFET串联而成,其中JFET的栅极连接到MOSFET的源极。MOSFET的漏源电压是JFET栅源电压的反相,从而使cascode 结构具有常见的常关特性。该结构可在额定漏源电压范围内阻断电流,但如同任何MOSFET(无论是硅基还是碳化硅基器件)一样,其反向电流始终可以流通。

图 1 Cascode配置

当内部MOSFET导通或有反向电流流过时,不论cascode的栅极电压如何,JFET的栅极-源极电压几乎为零,JFET处于导通状态。当MOSFET关断且cascode两端存在正的VDS(漏源电压)时,MOSFET的VDS会增加,与此同时JFET的栅源电压会降低至低于JFET的阈值电压,从而关断 JFET。请参见图1。

图 2 分立cascode结构

分立cascode 结构采用并排芯片,如图 2(a)所示,或堆叠芯片,如图 2(b)所示。在这两种情况下,SiC JFET 通常都是银烧结在封装引线框架上。

在并排配置中,MOSFET 安装在一个金属镀层的陶瓷隔离器上,有两组源极连接线:一组连接 JFET 源极和 MOSFET 漏极(金属镀层陶瓷的顶面),另一组连接 MOSFET 源极和源极引脚。在堆叠芯片配置中,JFET 源极和 MOSFET 漏极之间的连接线被取消,从而减少了杂散电感。并采用直径较小的连接线连接 JFET 和 MOSFET 栅极。

该MOSFET专为cascode结构设计,其有源区雪崩电压设定约为25V。MOSFET基于30V 硅工艺制造,具有低导通电阻RDS(on),通常仅为JFET的10%,并且具有低反向恢复电荷QRR等特性。JFET用于阻断高电压。大部分的开关和导通损耗都集中在JFET上。

图 3 Cascode正向和反向电流操作

Cascode的导通电阻RDS(on)包括 SiC JFET 和低压Si MOSFET 的导通电阻。cascode栅极关断时,反向电流流经 MOSFET 体二极管,从而自动导通 JFET,如图 3(b)所示的非同步反向电流情况。

在这种情况下,源极-漏极电压为 MOSFET 体二极管压降加上 JFET 导通电阻的压降。由于cascode内的 MOSFET 由硅制成,因此栅极关断时的源极-漏极电压不到同类 SiC MOSFET 的一半。当栅极导通时,cascode结构在正向和反向电流下具有相同的导通损耗。

Cascode的栅极电压范围非常灵活,原因有二。首先,栅极是 MOSFET 栅极,在室温下阈值电压接近 5 V,无需负栅极电压。栅极电压范围为±20 V,且不存在阈值电压漂移或迟滞风险,同时内置了栅极保护齐纳二极管。其次,cascode具有高增益。图 4 显示了采用 TOLL (MO-229) 封装的 750 V、5.4 mΩ第 4 代堆叠芯片结构的cascode—— UJ4SC075005L8S 在 25 °C的输出特性曲线。

图 4 Cascode的高增益可实现 10 V 栅极驱动

请注意,当cascode栅源电压超过约 8 V 时,其电导率的变化非常小。一旦MOSFET导通,JFET即完全导通。这意味着cascode可以用 0 至 10 V 的自举电压来驱动,从而最大限度地降低栅极驱动器的功率和成本。 另一方面,更宽的栅极电压范围(如 -5 至 +18 V)也不会对器件造成损害。

图 5 Cascode电容

图 5(a) 显示了 MOSFET 和 JFET 的芯片电容变化曲线。请注意,图 5(b) 中的 JFET 栅极电阻 RJG 并不是一个单独的电阻,而是 JFET 芯片的一部分。cascode与其他功率晶体管的一个主要区别是没有栅漏电容。当漏源电压VDS超过JFET阈值电压后,Crss实际上会降至零。这是因为 JFET 没有漏极-源极电容(既没有 PN 结,也没有体二极管来产生这种电容)。

这意味着在开关电压转换过程中,cascode的 dVDS/dt 主要由外部电路而不是cascode栅极电阻决定。Cascode的 MOSFET 开关速度可通过其栅极电阻调节,而 JFET 的开关速度部分由 MOSFET 决定,部分则由外部电路决定。这解释了为何在硬开关情况下,cascode结构需借助漏源缓冲电路(snubber)来控制关断速度并抑制电压过冲,下文将对此进行说明。所有 JFET 输出电容(包括栅漏电容与漏源电容)都是栅漏电容。cascode输出电容 Coss约等于 JFET 栅极-漏极电容。cascode输入电容 Ciss主要来自cascode的 MOSFET 栅极-源极电容。

Cascode结构的独特电容特性(图5)使其在开关过程中具有差异化的dVDS/dt行为:漏源电压转换速率主要由外部电路主导,而非栅极电阻。这一特性在硬开关场景中需配合缓冲电路(snubber)调控关断速度并抑制电压过冲。同时,其宽栅压兼容性(±20V)与高增益特性(图4)大幅降低了驱动复杂度,支持0-10V自举方案,为系统设计提供显著灵活性。

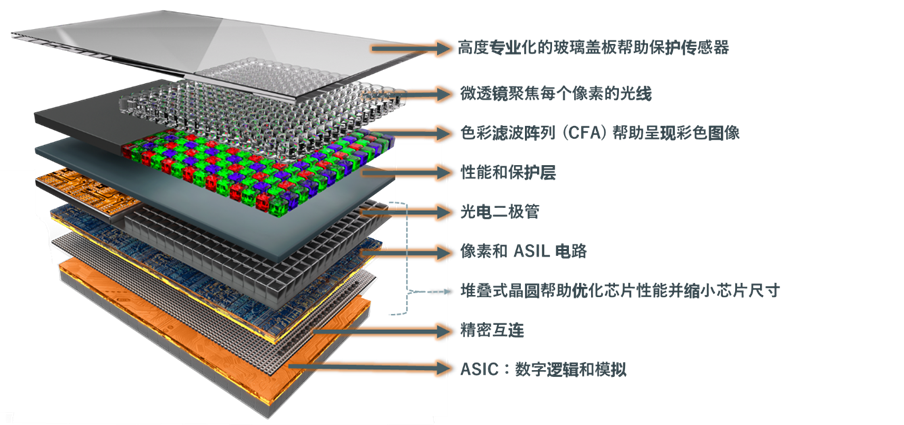

在技术创新的浪潮中,图像传感器的选型是设计与开发各类设备(涵盖专业与家庭安防系统、机器人、条码扫描仪、工厂自动化、设备检测、汽车等)过程中的关键环节。选择最适配的图像传感器需要对众多标准进行复杂的综合评估,每个标准都直接影响最终产品的性能和功能。从光学格式(Optical Format)和动态范围(Dynamic Range),到色彩滤波阵列(CFA)、像素类型、功耗及特性集成,这些考量因素多样且相互交织、错综复杂。

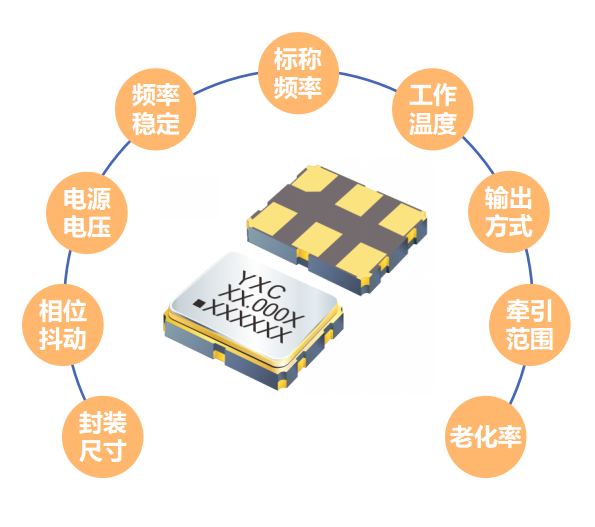

压控晶振(VCXO)作为频率调控的核心器件,已从基础时钟源升级为智能系统的"频率舵手"。通过变容二极管与石英晶体的精密耦合,实现电压-频率的线性转换,其相位噪声控制突破-160dBc/Hz@1kHz,抖动进入亚纳秒时代(0.15ps)。在5G-A/6G预研、224G光通信及自动驾驶多传感器同步场景中,VCXO正经历微型化(2016封装)、多协议兼容(LVDS/HCSL/CML集成)及温漂补偿算法的三重技术迭代。

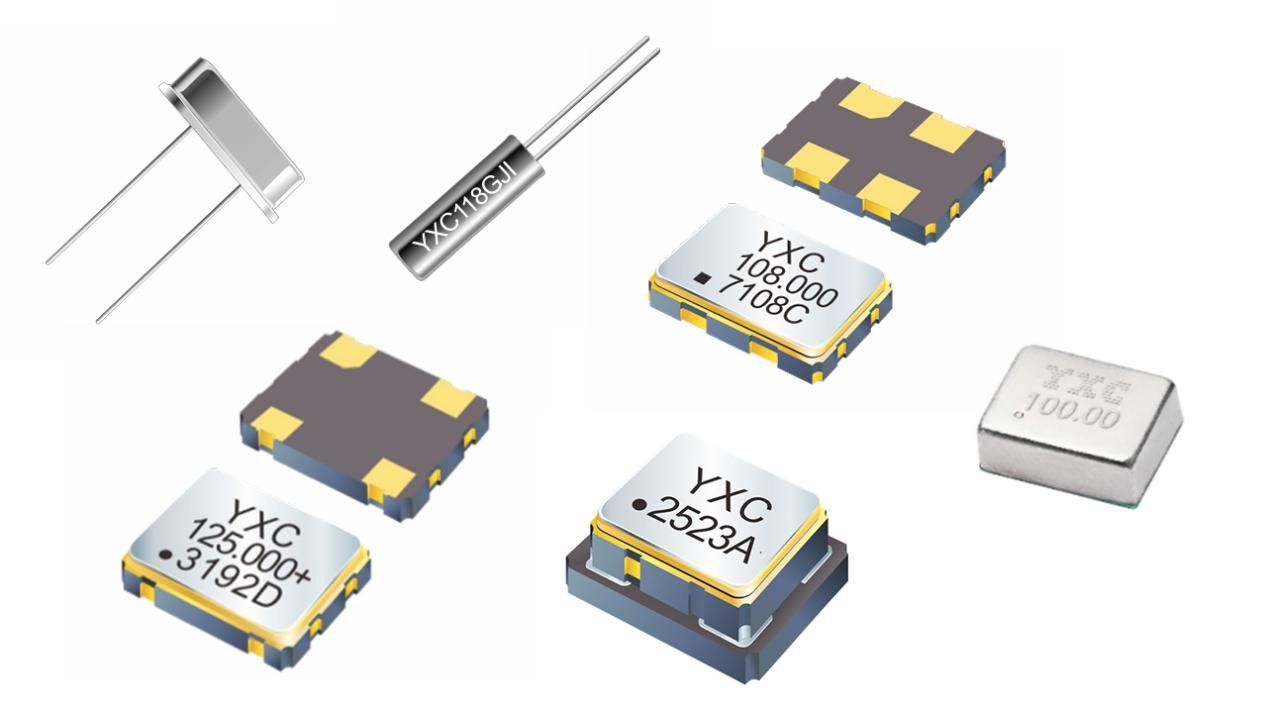

在电子设备的精密计时体系中,晶体振荡器与实时时钟芯片如同时间系统的"心脏"与"大脑":晶振通过石英晶体的压电效应产生基础频率脉冲,为系统注入精准的"生命节拍";而实时时钟芯片则承担时序调度中枢的角色,将原始频率转化为可追踪的年月日时分秒,并实现闹钟、断电计时等高级功能。二者协同构建现代电子设备的"时间维度"。

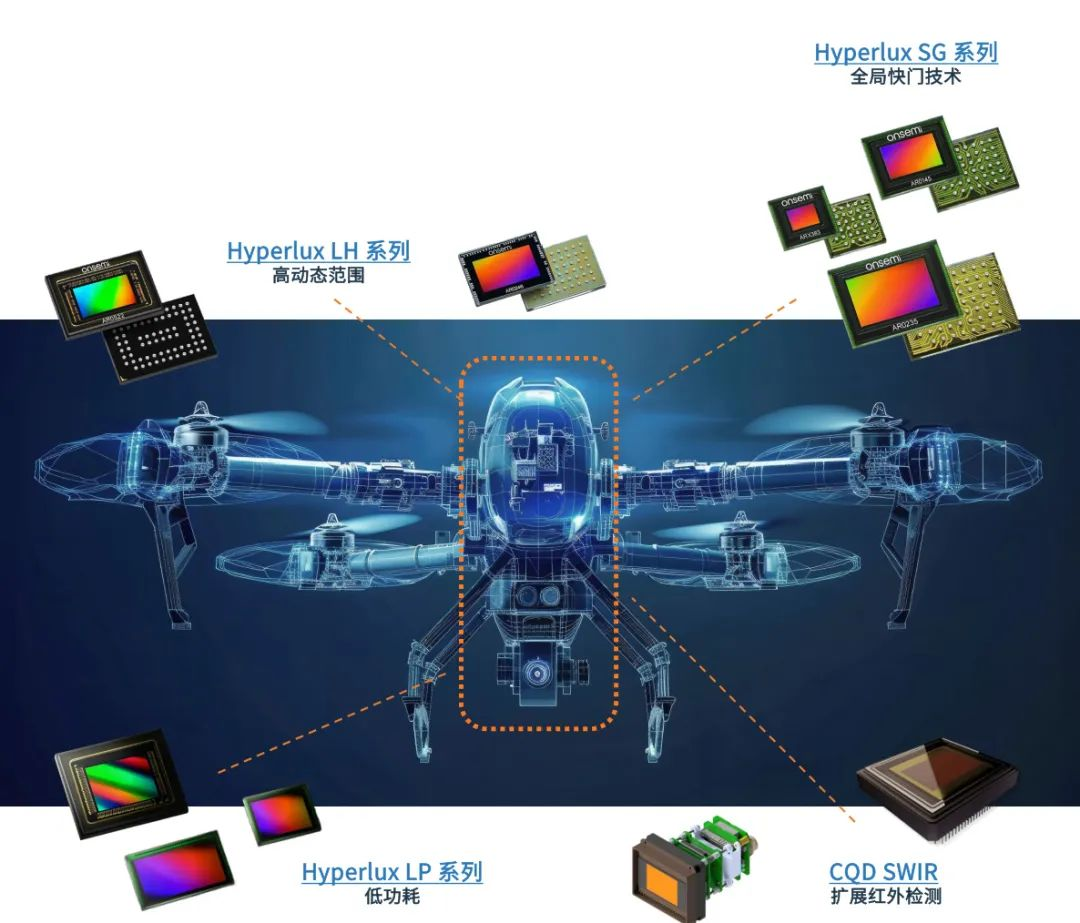

无人机已不再是简单的飞行器,而是集成了尖端感知与决策能力的空中智能载体。其核心系统——特别是自主导航与感知技术——是实现其在测绘、巡检、农业、物流、安防等多个领域高效、精准作业的关键。本文将深入剖析无人机如何通过这些核心技术“看见”、“思考”并“规划”路径,实现真正意义上的自主飞行能力。

压控晶体振荡器(Voltage-Controlled Crystal Oscillator, VCXO)是一种关键的高精度频率源,其核心特性在于能够通过施加外部控制电压来精细调节其输出频率。其频率控制过程依赖于精密的电路设计和晶体的独特物理特性,主要涉及以下核心原理: