发布时间:2025-05-7 阅读量:459 来源: 我爱方案网 作者:

【导读】全球EDA巨头Cadence公司于2025年5月7日正式宣布,其基于台积电3纳米(N3)制程的DDR5 MRDIMM Gen2内存IP解决方案已完成技术验证并投入商用。该方案实现了12.8Gbps的超高数据传输速率,较现行DDR5标准6400Mbps实现带宽翻倍突破,为AI训练、云端推理及高性能计算(HPC)提供了底层硬件支撑。

技术架构上,该方案整合了全新设计的PHY物理层与智能控制器子系统,通过硅验证的高性能架构实现了超低延迟(Ultra-Low Latency)与行业领先的RAS(可靠性、可用性、可服务性)特性。值得注意的是,其模块化设计支持SoC与小芯片(Chiplet)的灵活布局,允许根据应用场景对功耗和性能进行微调,特别适配异构计算场景需求。

在产业链协同方面,Cadence联合美光科技的1γ(1-gamma)DRAM颗粒与澜起科技的第二代MRCD/MDB接口芯片构建完整生态。美光副总裁Praveen Vaidyanathan指出,1γ工艺DRAM的存储密度较前代提升30%,结合Cadence IP可满足AI负载对高带宽和高可靠性的严苛要求。测试数据显示,该方案在典型AI推理任务中可实现能效比提升22%,内存延迟降低18%。

行业影响篇:重构数据中心内存技术标准

此次技术突破标志着三大产业趋势:

1. 工艺迭代驱动性能跃迁:台积电N3工艺采用FinFET结构优化方案,晶体管密度较5nm提升70%,为高频信号传输提供物理基础。Cadence通过DFM(面向制造的设计)技术实现12.8Gbps稳定运行。

2. 异构集成成为主流方向:MRDIMM Gen2采用Montage Technology的3D堆叠封装技术,通过TSV硅通孔实现多Rank并行访问,系统级带宽密度达到传统RDIMM的2.3倍。

3. AI工作负载定义硬件标准:该方案已应用于多家头部云服务商的AI加速卡设计,支持单卡千亿参数模型训练,预计2026年将带动AI服务器内存市场增长至380亿美元规模。

战略布局篇:构建下一代计算生态体系

Cadence通过三大举措巩固技术领导地位:

1. 全流程验证体系:集成VIP验证IP与DFI协议分析工具,实现从RTL设计到物理签核的全周期验证提速40%。

2. 开放合作模式:与台积电、三星共建2nm工艺设计套件(PDK),提前布局下一代Chiplet接口标准。

3. 垂直场景优化:针对自动驾驶推出车规级IP变体,满足ASIL-D功能安全认证,温度适应范围扩展至-40℃~125℃。

佰维存储2025年上半年实现营业收入3,912,336,913.69元,同比增长13.7%。但受行业周期等因素影响,公司报告期内归属于上市公司股东的净亏损为225,795,502.52元,同比由盈转亏;扣除非经常性损益后的净亏损为231,666,270.28元,同样出现同比下滑。业绩压力主要源于行业价格波动及公司战略性投入增加。

2025年上半年,工业富联(股票代码:601138.SH)实现营业收入3607.6亿元,同比大幅增长35.58%;归属于上市公司股东的净利润达121.13亿元,同比增长38.61%;扣非净利润116.68亿元,同比增长36.73%,核心财务指标均创历史新高。报告期内,公司总资产规模增至3831.28亿元,同比增长20.66%,展现出强劲的资产扩张能力。

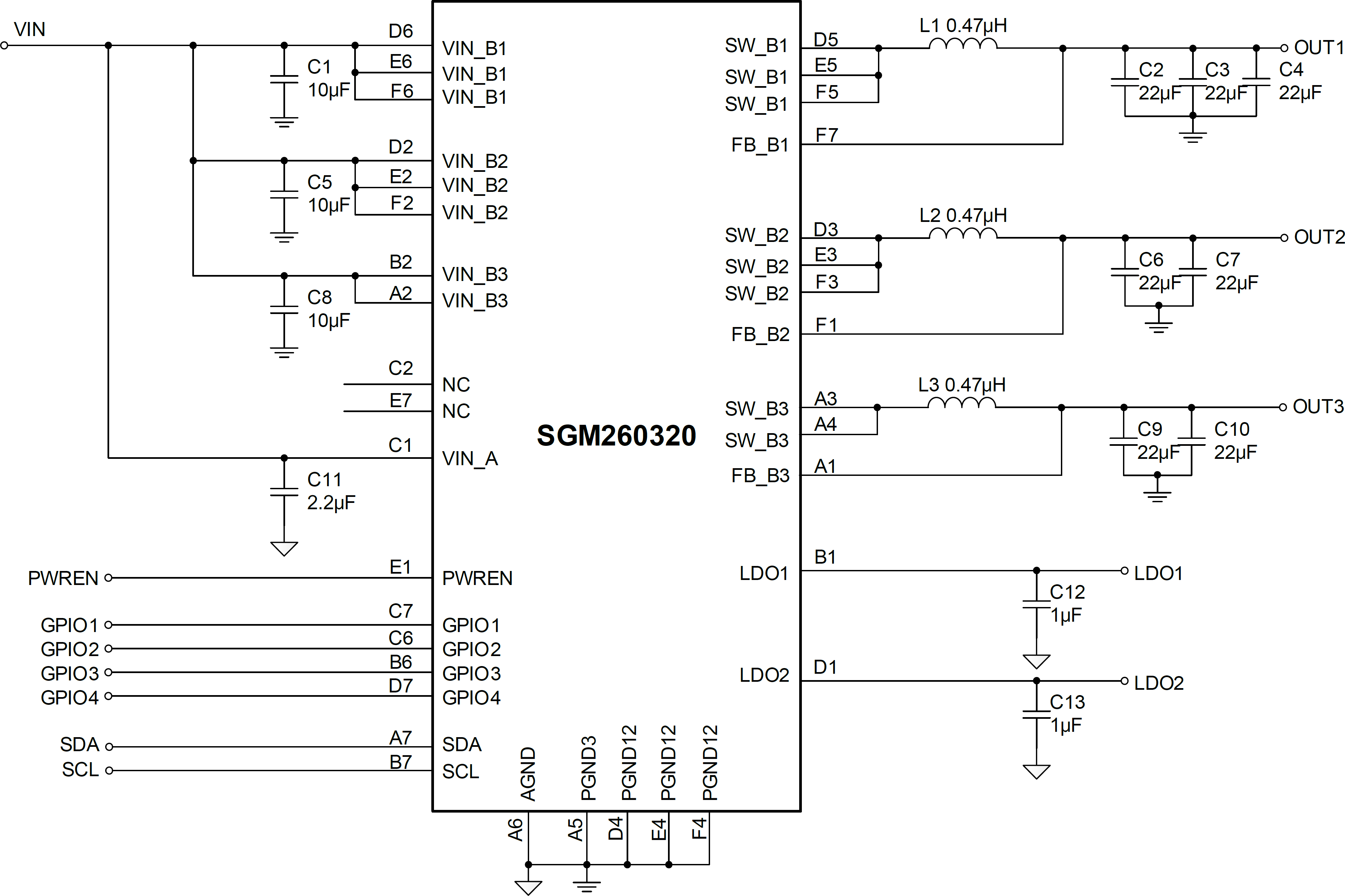

在追求电子设备小型化、高性能和超低功耗的时代,复杂的多轨电源设计已成为研发的关键挑战。传统分立式电源方案不仅占用宝贵的PCB面积,也增加了设计难度与系统功耗控制的复杂性。固态硬盘(SSD)、现场可编程门阵列(FPGA)、微控制器单元(MCU)系统及便携设备对电源管理集成电路(PMIC)的要求日益严苛:高效转换、低待机功耗、高集成度、精确调压以及智能化管理缺一不可。圣邦微电子(SG Micro)推出的SGM260320 PMIC,正是瞄准这一市场需求,以高度集成、卓越性能和丰富的可配置功能,提供了一站式的高效供电解决方案。

随着智能手机影像功能逐渐成为用户核心需求,光学防抖(OIS)技术正面临前所未有的性能挑战。TDK株式会社凭借旗下InvenSense公司15年OIS/EIS技术积累,最新推出的SmartMotion® ICM-536xx系列六轴IMU,正在打破高端防抖技术的成本壁垒。该方案通过突破性的6.4kHz输出数据速率和20位分辨率,首次将专业级防抖性能引入主流移动设备市场。

2024年,全球工业机器人市场经历了一次明显的周期性调整。国际机器人联合会(IFR)的初步统计数据显示,全年新装机量约为52.3万台,较上年下滑约3%。这是近年来该市场罕见出现的负增长,反映出多重经济与技术周期叠加下的复杂局面。