发布时间:2025-04-30 阅读量:4103 来源: 我爱方案网 作者:

【导读】在2025年北美技术研讨会上,台积电正式宣布其A14(1.4nm)工艺将于2028年量产,并明确表示无需依赖ASML最新一代High NA EUV光刻机。这一决策背后,折射出全球半导体巨头在技术路线、成本控制和市场竞争中的深层博弈。

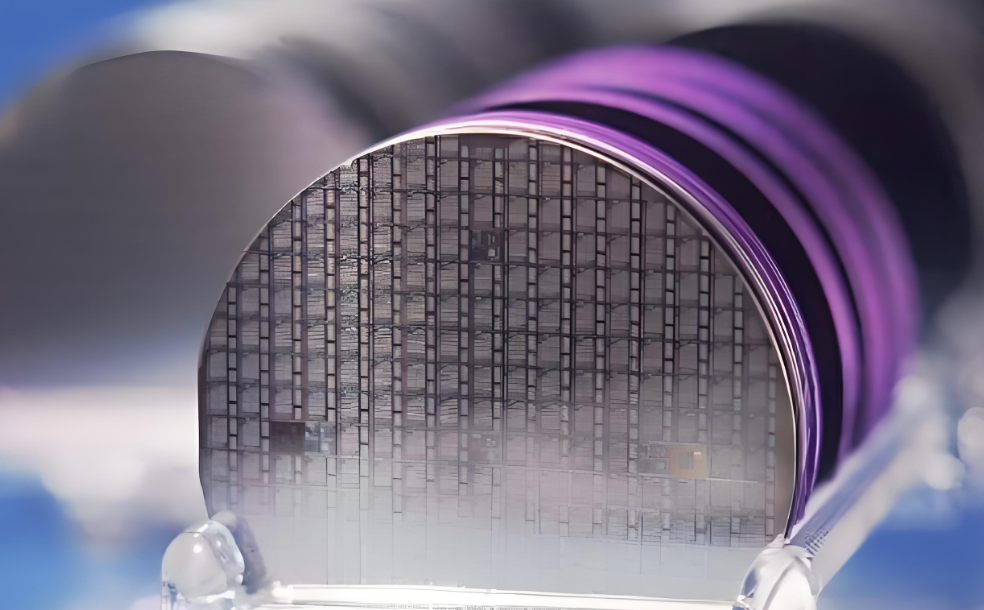

技术路径:台积电的"多重曝光"创新

台积电通过优化现有Low NA EUV光刻机的多重图案化技术,实现了从2nm到A14节点的持续微缩。数据显示,A14工艺在相同功耗下速度提升15%,逻辑密度增加20%,且良率表现超预期。其核心突破在于第二代GAA晶体管架构与NanoFlex Pro设计协同技术,允许芯片设计者灵活调整晶体管配置以实现性能、功耗和面积的平衡。相比之下,英特尔则押注High NA EUV技术,计划在2025年将首批发货的High NA设备投入18A制程量产,并声称其生产效率比传统EUV提升2倍。

成本博弈:光刻机定价的"双刃剑"

ASML的High NA EUV设备单价高达3.8亿美元,是传统EUV的2.1倍。台积电通过大规模采购Low NA设备(2024-2025年订购超60台)摊薄成本,而英特尔虽抢先获得首台High NA设备,却需承担高昂的研发调试费用。值得关注的是,台积电通过议价使首台High NA设备采购价低于ASML报价27.5%,凸显其供应链话语权。三星则采取折中策略,计划2027年将High NA技术商用化,但初期仅用于研发。

竞争动态:代工市场的技术分水岭

英特尔通过High NA布局试图弯道超车,其14A节点将全面采用该技术,预计使晶体管密度提升2.9倍。而台积电选择在2029年推出的A14P工艺中引入High NA,同时开发背面供电技术(Super Power Rail),形成技术储备。三星则面临双重压力:既要追赶台积电的制程进度,又需应对High NA带来的晶圆厂改造挑战。三方博弈下,ASML的产能分配成为关键变量——2025年High NA设备年产量仅20台,英特尔已锁定半数以上。

未来布局:技术迭代的生态重构

台积电的延迟采用策略基于对产业生态的深度考量。当前90%的EUV设备集中于其晶圆厂,形成成熟的技术验证体系。而High NA的全面普及需要配套光刻胶、掩膜检测等产业链升级,ASML预计2030年才能实现Hyper NA(0.75数值孔径)设备商用。这种技术代际差为台积电创造了缓冲期,使其可通过A14X高性能版本(2029年)和CoWoS先进封装技术维持竞争优势。

近期,围绕英特尔首席执行官陈立武的任职资格问题,美国政界刮起一阵强风。事件源于美国参议员汤姆·科顿(Tom Cotton)本月5日致函英特尔董事会,对陈立武在华投资历史及其潜在利益冲突提出尖锐质疑,认为这可能危及英特尔获得的美国政府巨额补贴(包括《芯片与科学法案》下的近80亿美元)所应承担的国家安全责任,尤其涉及敏感的“安全飞地”(Secure Enclave)国防芯片项目。此质疑引发了广泛关注。

2025年8月7日,中国半导体行业领军企业中芯国际和华虹半导体正式发布2025年第二季度业绩报告。数据显示,两家企业销售收入均实现高两位数增长,并带动盈利能力大幅提升。这一成绩不仅体现了国内晶圆制造领域的高效运营,还反映出全球半导体需求的稳健复苏。分析机构指出,在人工智能、汽车电子和5G通信技术的推动下,中国半导体企业正通过优化产线和扩产战略,持续提升市场竞争力。

三星电子最新一代折叠屏智能手机Galaxy Z Fold 7与Galaxy Z Flip 7甫一上市,即在全球多地区域引发显著消费热潮。最新数据显示,在俄罗斯这一三星曾战略退出的关键市场,该系列的预售表现超出预期。行业分析机构透露,相较于前代产品,Z7系列在俄罗斯的预订量实现了约30%的显著提升。值得关注的是,采用超薄设计、轻量化大幅改进的Galaxy Z Fold 7在俄预售中占据主导,份额高达约70%,充分体现了消费者对于产品形态革新突破的高度认可。

2025年8月,全球模拟芯片龙头德州仪器(TI)对中国客户启动覆盖超6万款产品的价格调整,涨幅达10%-30%,远超6月仅3300款产品的定向调价规模。尽管官方通知生效日为8月15日,部分客户反馈新定价已于8月4日提前执行。此次涨价涵盖工业控制、汽车电子、消费电子及通信设备全品类,其中41.3%的产品涨幅超30%,工业级数字隔离器和车规电源管理芯片(PMIC)成为重灾区,涨幅普遍超过25%。

2025财年第一季度,日本罗姆半导体(ROHM)面临严峻财务挑战:营收同比下滑1.8%至1162亿日元,营业利润暴跌84.6%至1.95亿日元。尽管净利润下滑14.3%,但公司成功结束连续三季亏损,实现扭亏为盈。业绩承压主因工业机械与汽车应用领域需求疲软(销售额分别下降5%和7%),叠加中国碳化硅(SiC)厂商的竞争冲击。