发布时间:2025-04-15 阅读量:805 来源: Cadence 发布人: wenwei

【导读】2025年4月,Cadence与台积电(TSMC)联合宣布,基于台积电最新N3P工艺节点的嵌入式USB2版本2(eUSB2V2)IP解决方案成功流片,标志着现代计算设备接口技术的重大突破。该方案整合了PHY IP与控制器IP,支持高达4.8Gbps的数据传输速率,较传统USB 2.0提升十倍,为AI PC、4K视频处理、物联网及5G通信设备提供高效能连接支持。

技术亮点与工艺优势

eUSB2V2标准于2024年9月发布,专为应对先进制程(5纳米及以下)的低电压(<1.2V)需求设计,解决了传统USB 2.0在3.3V高电压下的工艺兼容性问题,显著降低功耗并提升能效。台积电N3P工艺通过光学微缩技术,相较于前代N3E,在相同功耗下性能提升4%或功耗降低9%,同时优化了生产成本与良率,成为AI芯片与高性能计算的首选工艺。Cadence的解决方案在此工艺基础上,进一步支持非对称链路模式(4.8Gbps)与对称配置(960Mbps至4.8Gbps),满足多样化场景需求。

应用场景与市场影响

随着AI驱动的计算、高分辨率摄像头及实时数据处理需求激增,传统接口带宽瓶颈日益凸显。eUSB2V2的推出将支持4K/8K视频无缝传输、增强现实(AR)应用流畅运行,并释放AI设备潜力,例如智能摄像头、边缘计算模块及5G基站。此外,该IP方案通过增强抗电磁干扰(EMI)能力与可扩展链路配置,为紧凑型物联网设备设计提供灵活性。

合作背景与行业认可

Cadence与台积电的长期合作覆盖3D-IC、先进封装及IP开发,此次eUSB2V2 IP的流片是双方在N3P节点上的又一里程碑。台积电北美子公司高管Lluis Paris指出,此次合作体现了双方对技术前瞻性与产业需求的精准把握。目前,已有客户将该IP集成至新一代计算设备SoC中,预计2025年下半年搭载该技术的终端产品将陆续上市。

未来展望

eUSB2V2 IP的推出不仅填补了传统USB与高速接口间的技术鸿沟,更推动了半导体工艺与系统设计的协同创新。随着台积电N3P工艺的大规模应用,Cadence的IP生态将进一步加速AI、超算及消费电子领域的性能升级,为全球科技产业注入新动能。

Diodes公司近期公布了截至2025年6月30日的第二季度财务业绩,标志着其连续三个季度实现同比增长,显示出半导体市场的稳步复苏。根据报告,该公司在多个关键财务指标上表现稳健,受益于全球需求的逐步回升和市场结构优化。公司高层认为,这一业绩源于亚洲地区的强劲拉动和产品组合的适应性调整。

美国射频半导体龙头企业MACOM Technology Solutions于8月7日正式公布截至2025年7月4日的第三财季业绩报告。财报显示,当季实现营收2.521亿美元,较去年同期大幅增长32.3%,创下近三年最高单季增速。

美国微芯科技公司(Microchip Technology)于8月7日发布了其2026财年第一季度(截至2025年6月30日)的财务报告。报告显示,公司业绩呈现显著复苏迹象,多项关键指标环比改善,并超出此前修订后的业绩指引。

8月8日,赛力斯集团(601127)公布2025年7月产销快报。数据显示,尽管整体市场仍承压,集团在主力新能源汽车板块显现增长韧性,单月销量同比提升5.7%,而传统燃油车型业务持续收缩,反映出业务转型的深化推进。

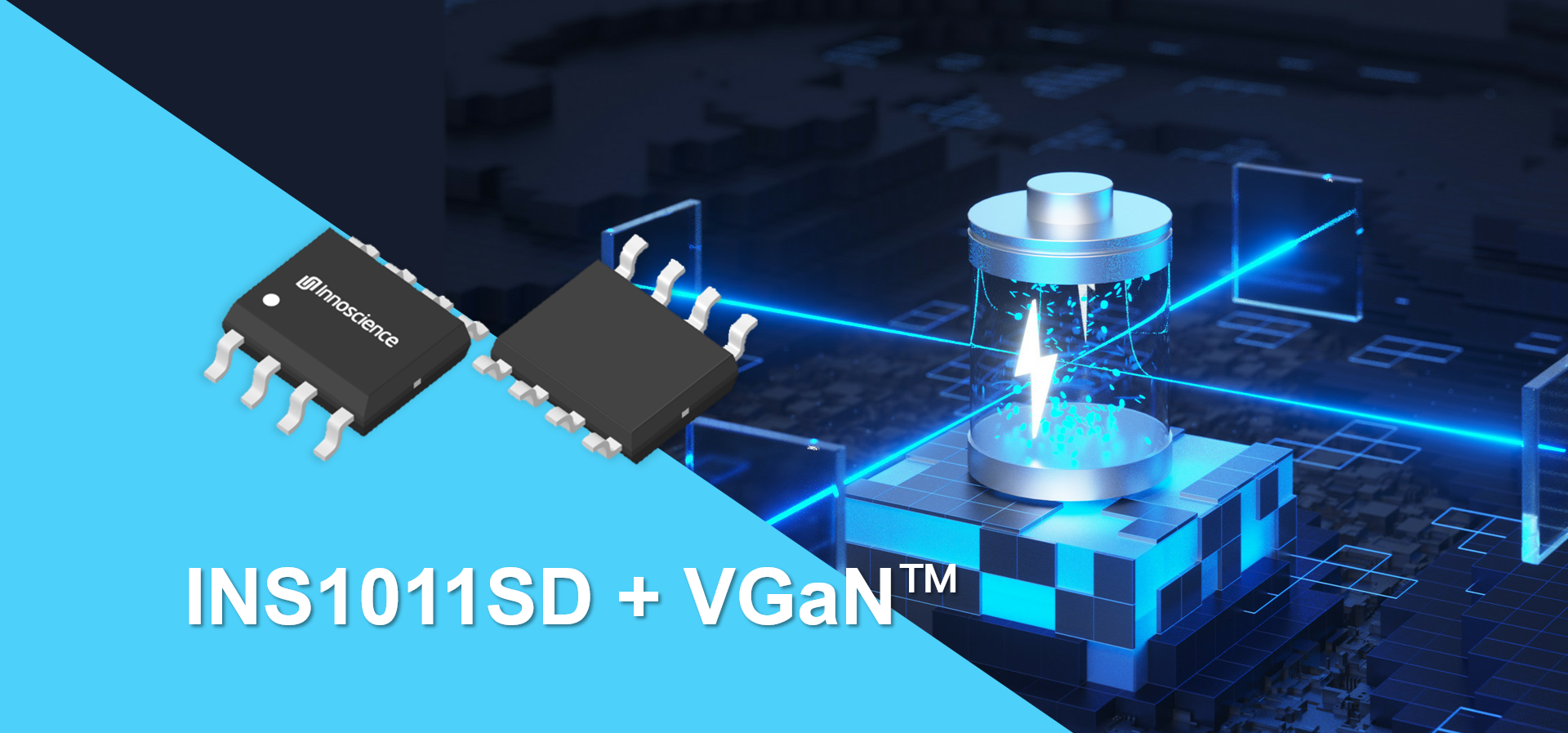

在追求更高效率、更小体积和更低成本的电力电子系统发展趋势下,传统的硅基(Si)功率器件,特别是在双向能量流动应用(如电池管理系统BMS)中常用的背靠背MOSFET方案,逐渐显现出性能瓶颈。氮化镓(VGaN™)器件凭借其卓越的开关速度、低导通电阻和更小的尺寸,成为理想的替代者。然而,充分发挥VGaN™的潜力需要与之高度匹配的专用驱动芯片。英诺赛科(Innoscience)作为全球领先的VGaN™ IDM厂商,推出全球首款100V低边驱动芯片INS1011SD,标志着“VGaN™+专用驱动”完整解决方案的成熟,为双向电力电子系统设计带来革命性突破。