发布时间:2024-07-2 阅读量:3381 来源: 综合自网络 发布人: wenwei

【导读】共模电感(Common mode Choke),也叫共模扼流圈,常用于电脑的开关电源中过滤共模的电磁干扰信号。在板卡设计中,共模电感也是起EMI滤波的作用,用于抑制高速信号线产生的电磁波向外辐射发射。

一、设计因素

在一些主板上,我们能看到共模电感,但是在大多数主板上,我们都会发现省略了该元件,甚至有的连位置也没有预留。这样的主板,合格吗?

不可否认,共模电感对主板高速接口的共模干扰有很好的抑制作用,能有效避免EMI通过线缆形成电磁辐射影响其余外设的正常工作和我们的身体健康。但同时也需要指出,板卡的防EMI设计是一个相当庞大和系统化的工程,采用共模电感的设计只是其中的一个小部分。高速接口处有共模电感设计的板卡,不见得整体防EMI设计就优秀。所以,从共模滤波电路我们只能看到板卡设计的一个方面,这一点容易被大家忽略,犯下见木不见林的错误。

只有了解了板卡整体的防EMI设计,我们才可以评价板卡的优劣。那么,优秀的板卡设计在防EMI性能上一般都会做哪些工作呢?

1.主板Layout(布线)设计

对优秀的主板布线设计而言,时钟走线大多会采用屏蔽措施或者靠近地线以降低EMI。对多层PCB设计,在相邻的PCB走线层会采用开环原则,导线从一层到另一层,在设计上就会避免导线形成环状。如果走线构成闭环,就起到了天线的作用,会增强EMI辐射强度。

信号线的不等长同样会造成两条线路阻抗不平衡而形成共模干扰,因此,在板卡设计中都会将信号线以蛇形线方式处理使其阻抗尽可能的一致,减弱共模干扰。同时,蛇形线在布线时也会最大限度地减小弯曲的摆幅,以减小环形区域的面积,从而降低辐射强度。

在高速PCB设计中,走线的长度一般都不会是时钟信号波长1/4的整数倍,否则会产生谐振,产生严重的EMI辐射。同时走线要保证回流路径最小而且通畅。对去耦电容的设计来说,其设置要靠近电源管脚,并且电容的电源走线和地线所包围的面积要尽可能地小,这样才能减小电源的纹波和噪声,降低EMI辐射。

当然,上述只是PCB防EMI设计中的一小部分原则。主板的Layout设计是一门非常复杂而精深的学问,甚至很多DIYer都有这样的共识:Layout设计得优秀与否,对主板的整体性能有着极为重大的影响。

2.主板布线的划断

如果想将主板电路间的电磁干扰完全隔离,这是绝对不可能的,因为我们没有办法将电磁干扰一个个地“包”起来,因此要采用其他办法来降低干扰的程度。主板PCB中的金属导线是传递干扰电流的罪魁祸首,它像天线一样传递和发射着电磁干扰信号,因此在合适的地方“截断”这些“天线”是有用的防EMI的方法。“天线”断了,再以一圈绝缘体将其包围,它对外界的干扰自然就会大大减小。如果在断开处使用滤波电容还可以更进一步降低电磁辐射泄露。这种设计能明显地增加高频工作时的稳定性和防止EMI辐射的产生,许多大的主板厂商在设计上都使用了该方法。

3.主板接口的设计

不知大家是否注意到,主板都会附送一块开口的薄铁挡片,其实这也是用来防EMI的。虽然机箱EMI屏蔽性能都不错,但电磁波还是会从机箱表面的开孔处泄漏出来,如PS/2接口、USB接口以及并、串口等的开口处。孔的大小决定了电磁干扰的泄露程度。开口的孔径越小,电磁干扰辐射的削弱程度越大。对方形孔而言,L就是其对角线长度。

使用了挡片之后,挡片上翘起的金属触片会和主板上的输入输出部分很好地通过机箱接地,不但衰减了EMI,而且减小了方孔的尺寸,进一步缩小L值,从而可以更有效地屏蔽电磁干扰辐射。

上述三点只是主板设计中除电路设计之外的几个主要防EMI设计,由此可见,主板的防EMI设计是一个整体的概念,如果整体的设计不合格,就会带来较大的电磁辐射,而这些也不是一个小小的共模电感所能弥补的。

二、共模电感的选型

对于电源线路,其共模噪声的来源相对比较明确,只是杂散因素难以通过仪器测量,大多数情况下是依赖试验后再进行分析的方式来逐步逼近结果,因此累积的经验非常重要。上一期文章在介绍共模电感的应用时,已经讲到理论上对共模噪声的幅度预估和对应的共模电感的感量需求,可以作为早期试验的出发点。

通常情况下,适用在AC-DC电源输入端的滤波阶段的共模电感采用了闭合磁路的磁环作为磁芯,这样做的好处是可以轻松实现非常低的漏感和非常高的耦合系数,对于高输入电压和相对低的开关频率而言可以提供不错的高共模阻抗来抑制较高幅值的共模噪声幅度。由于磁性材料的磁导率可以分为感性部分μr'和损耗部分μr'',在磁芯接近或者高于阻抗特性最高点时,损耗部分将占据阻抗的主要部分,这时的噪声抑制不再是通过感抗来降低噪声幅度,而是通过损耗发热的形式将噪声能量吸收,因此适当的(过度饱和将导致阻抗降低)饱和程度并不会影响噪声的抑制效果,使得我们在挑选共模电感时不必去寻找类似于功率电感中的饱和电流参数。

同时,如果漏感的部分,比如1mH的电感耦合系数99%那么将会有10uH的漏感存在于差分线路上,当考虑差模噪声抑制(通常是LC滤波桥)时,这一部分漏感也需要考虑在内。适量的漏感对于高频差模噪声抑制有帮助,但是因为共模电感基本上采用的是磁路闭合磁芯,很容易导致在大电流时磁芯饱和,这对电源转换效率和滤波噪声带宽都有影响。提高漏感的占比通常可以选用方形或者框架磁芯结构(UU磁芯或者PQ磁芯等),也可以通过非对称绕组( L1≠L2 )来实现,具体的选择需要用户通过差共模分离器鉴别测试后决定是否必要。

对于共模电感的参数而言,主要包括单边感值、Rdc、额定电流、额定电压和耐压Hi-pot。其中单边感值主要决定了共模阻抗的大小,Rdc是导线的直流损耗,接着损耗带来的温升就产生了额定的电流的限额,最后因为使用在高压线路上所以电压限额和安规要求分别标出。但是用户更希望评估的还是滤波效果,所以一般情况下规格书会提供两种形式的阻抗特性曲线,一是如图Fig.3-a所示的共模/差模阻抗形式,二是如图Fig.3-b所示的插入损耗dB形式,两者是对等的,插入损耗dB形式的曲线是将共模/差模阻抗折算到50Ω+50Ω的系统内形成的。

【Fig.3(a) 共模/差模阻抗形式】

【Fig.3(b)插入损耗dB形式】

对于同一个共模系列,不同尺寸的封装结构适用不同的电流大小和滤波带宽:尺寸越大,磁芯可以具有更低的磁阻,从而可以减少绕组匝数,这样铜线的线径可以放大,因此可以适用更大的电流回路;感值越高或者材料磁导率稳定频率越低,则适用的滤波带宽更窄,这样的共模电感放到回路上很可能对高频端没有噪声抑制效果。

推荐阅读:

Seal Ring,中文常译为“密封环”或“保护环”,是位于芯片最外层的一圈特殊结构,通常由多层金属和介质材料构成,环绕在芯片有源电路区域(即核心功能模块)的四周。它并非用于信号传输或数据处理,而是作为一种物理和电气的“防护屏障”,主要作用是保护芯片内部精密的电路结构免受外部环境和制造工艺的影响。

14名犯罪嫌疑人因非法获取、泄露华为公司商业秘密,被法院依法判处有期徒刑。

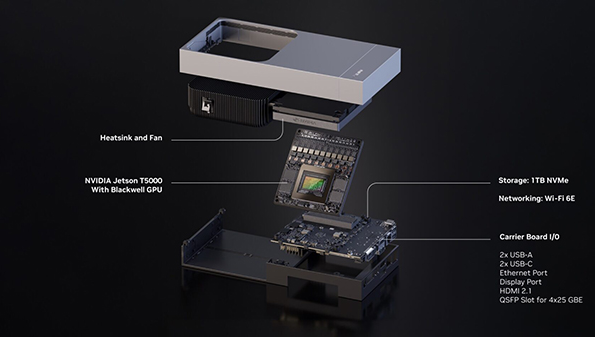

全球人工智能与机器人领域迎来又一里程碑事件,芯片巨头英伟达(NVIDIA)正式发布了其新一代机器人计算平台——Jetson Thor系列。该芯片并非此前Jetson Orin系列的简单迭代,而是基于NVIDIA Thor SoC(系统级芯片)打造,专为性能密集型仿人机器人和自主机器设计,被业界誉为“迄今性能最强的机器人专用芯片”。它的发布,标志着具身智能(Embodied AI)向大规模、复杂化应用迈出了关键一步。

在电子电路设计与系统保护中,TVS管(瞬态电压抑制二极管)和稳压二极管(又称齐纳二极管)是两种常见且功能各异的半导体器件。尽管它们在外部形态和电路符号上较为相似,但二者的工作原理、核心参数及应用场景存在本质区别。本文将从多个维度系统分析TVS管与稳压二极管的区别,帮助工程师做出正确的选型决策。

在追求更高效率、更高功率密度的电力电子系统设计中,碳化硅(SiC)MOSFET已成为不可或缺的核心器件。英飞凌科技推出的第二代CoolSiC™ MOSFET(G2)技术,以其卓越的性能,为光伏逆变器、储能系统、电动汽车充电桩及工业驱动等应用树立了新的标杆。