发布时间:2024-06-17 阅读量:1843 来源: 综合自网络 发布人: wenwei

【导读】寄生电容有一个通用的定义:寄生电容是存在于由绝缘体隔开的两个导电结构之间的虚拟电容(通常不需要的),是 PCB 布局中的一种效应,其中传播的信号表现得好像就是电容,但其实并不是真正的电容。寄生电容通常出现在被电介质隔开的任何一对导体之间。

一、什么导致寄生电容?

在高频下,电路板中的电流受到寄生电容的影响。因为当频率增加时,电容器往往会变成导体。请注意,当频率增加时,电容器将充当值非常小的电阻器(接近短路),导致电流过大。

ZC= 1/2πfC;FC= 1/ωC因此,随着频率的增加,ZC也增加。

寄生电容会在高频操作期间让您发冷,因为电容器在无限频率下就像一根电线。这就是为什么它会意外地将任何 PCB 的参考平面连接到机箱的原因。

寄生电容效应可能是串扰和噪声、来自输出的不良反馈以及谐振电路的形成。因此,必须注意整体印刷电路板设计,特别是布局。在将一个导电体放置在另一个导电体的旁边时,良好的布局应格外小心。

二、PCB 寄生电容的影响

(1)传输线中的频带限制行为,在非常高的频率下产生低通滤波器行为。

(2)不同电位地之间的噪声耦合,导致共模噪声。

(3)噪声或信号耦合到组件中,尤其是绕线电感。

(4)高频电容串扰(表现为 FEXT 和 NEXT)。

(5)由于电源层和接地层之间的间距而导致的 PDN 阻抗修改。

(6)EMI 耦合到散热器中,产生共模电流。

三、PCB 寄生电容怎么消除?

PCB 布局永远不会完全消除寄生电容,但你可以减少PCB 布局中的寄生电容或者采取一些措施来限制寄生电容对信号和电源完整性的影响。这里列举9条可以减少 PCB 布局中的寄生电容的措施:

1、避免平行布线

采用平行布线时,金属之间的面积最大,寄生电容也会最大。

2、移除电源层

电源层通常被认为是交流接地,与接地层完全相同,所以移除电源层与移除导体附近的接地层一样重要。

3、使用法拉第屏蔽或保护环

将法拉第屏蔽放置在两条迹线之间以最大程度地减少寄生电容效应。

4、关键走线尽可能窄和短

为了最大限度地减少寄生电容,使关键走线尽可能窄,以使 PCB 工艺可以处理,与附近的走线保持良好的距离。

5、避免过度使用过孔

过孔的过度使用会增加寄生电容,最好尽可能用贴片来代替过孔。

6、避免元件分离

元件之间、电源层和接地层,输出和输入等的正确接线,对减少不需要的寄生电容非常重要。

7、信号层应该夹在两个地平面之间,或者夹在一个地平面或一个电源平面之间

在 4 层板中,您可以将电源平面放置在底层,并在电源平面和接地平面之间布置一些敏感的走线。这将防止来自一层信号的 EMI 引起另一层信号中的噪声。

8、确定正确的层厚

较薄的层会减少环路面积和寄生电感,但会增加寄生电容。您可以使用具有不同层堆栈的模拟工具来确定正确的层厚度。

9、阻抗匹配

在高速数字应用中,多条数据线以数十 Gbps 的速度运行,由于寄生电容和电感而导致阻抗不匹配。寄生效应引起的任何不匹配都会在线路上的某处产生反射,最终增加时序抖动和误码率。传输高速数据的信号线的阻抗应该匹配。

佰维存储2025年上半年实现营业收入3,912,336,913.69元,同比增长13.7%。但受行业周期等因素影响,公司报告期内归属于上市公司股东的净亏损为225,795,502.52元,同比由盈转亏;扣除非经常性损益后的净亏损为231,666,270.28元,同样出现同比下滑。业绩压力主要源于行业价格波动及公司战略性投入增加。

2025年上半年,工业富联(股票代码:601138.SH)实现营业收入3607.6亿元,同比大幅增长35.58%;归属于上市公司股东的净利润达121.13亿元,同比增长38.61%;扣非净利润116.68亿元,同比增长36.73%,核心财务指标均创历史新高。报告期内,公司总资产规模增至3831.28亿元,同比增长20.66%,展现出强劲的资产扩张能力。

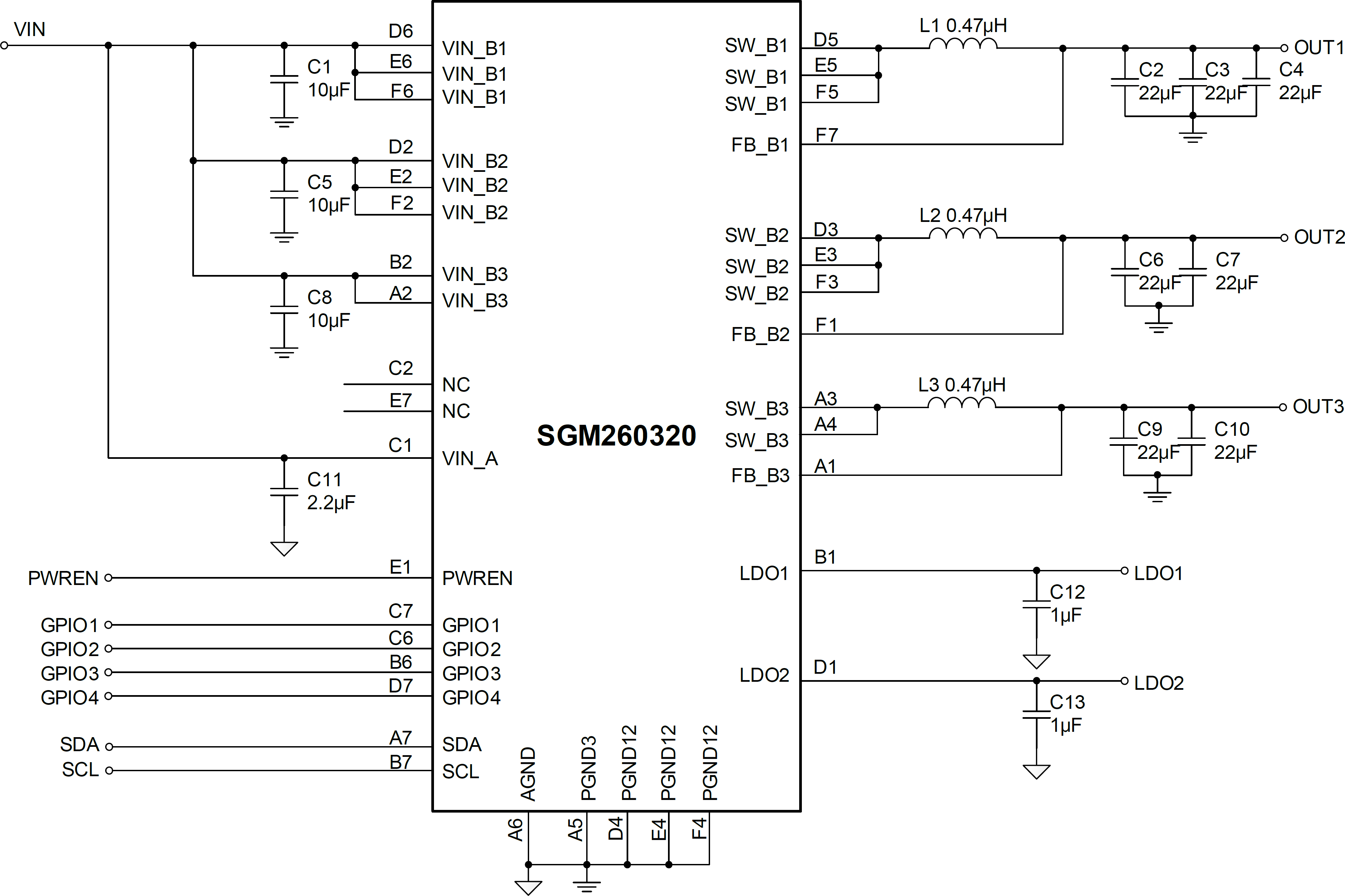

在追求电子设备小型化、高性能和超低功耗的时代,复杂的多轨电源设计已成为研发的关键挑战。传统分立式电源方案不仅占用宝贵的PCB面积,也增加了设计难度与系统功耗控制的复杂性。固态硬盘(SSD)、现场可编程门阵列(FPGA)、微控制器单元(MCU)系统及便携设备对电源管理集成电路(PMIC)的要求日益严苛:高效转换、低待机功耗、高集成度、精确调压以及智能化管理缺一不可。圣邦微电子(SG Micro)推出的SGM260320 PMIC,正是瞄准这一市场需求,以高度集成、卓越性能和丰富的可配置功能,提供了一站式的高效供电解决方案。

随着智能手机影像功能逐渐成为用户核心需求,光学防抖(OIS)技术正面临前所未有的性能挑战。TDK株式会社凭借旗下InvenSense公司15年OIS/EIS技术积累,最新推出的SmartMotion® ICM-536xx系列六轴IMU,正在打破高端防抖技术的成本壁垒。该方案通过突破性的6.4kHz输出数据速率和20位分辨率,首次将专业级防抖性能引入主流移动设备市场。

2024年,全球工业机器人市场经历了一次明显的周期性调整。国际机器人联合会(IFR)的初步统计数据显示,全年新装机量约为52.3万台,较上年下滑约3%。这是近年来该市场罕见出现的负增长,反映出多重经济与技术周期叠加下的复杂局面。