发布时间:2023-04-4 阅读量:764 来源: 我爱方案网 作者: bebop

Chiplet是将一类满足特定功能的die,通过die-to-die内部互联技术实现多个模块芯片与底层基础芯片封装在一起,进而形成一个系统芯片。它能在不改变制程的前提下提升芯片集成度,提高算力并保证芯片生产良率,相比传统SoC在设计灵活度、设计与生产成本、上市周期等方面优势明显,有望成为后摩尔时代我国集成电路弯道超车的重要途径。

资料显示,Chiplet可在不改变制程的前提下提升算力,且保证芯片良率。Chiplet俗称“芯粒”,又称“小芯片组”,从字面意义上可以理解为“粒度更小的芯片”。它是将一类满足特定功能的die,通过die-to-die内部互联技术实现多个模块芯片与底层基础芯片封装在一起,进而形成一个系统芯片。它可以有效提升芯片的集成度,是在不改变制程的前提下提升算力,并且保证芯片生产良率的一种手段。

目前,Chiplet市场规模正不断扩张,预计2034年有望达到570亿美元。Chiplet可在一定程度上避免摩尔定律放缓的窘境,全球半导体龙头企业积极推进,市场规模有望实现高速增长。Omdia指出,2018年全球Chiplet市场规模约为6.45亿美元,至2024年将达到58亿美元,预计到2035年有望突破570亿美元,2018-2035年复合增长率超过30%。

Chiplet的多种优势

与传统SoC相比,Chiplet在设计灵活度、设计与生产成本、上市周期等方面优势明显。传统SoC,即系统级单芯片,是将多个负责不同类型计算任务的计算单元,通过光刻的形式制作到同一块晶圆上。随着摩尔定律放缓,传统的SoC的生产周期越来越长,在成本大幅增加的情况下性能提升幅度有限,行业接近制造瓶颈;与SoC不同,Chiplet是将一块原本复杂的SoC芯片,从设计时就先按照不同的计算单元或功能单元对其进行分解,然后每个单元选择最适合的半导体制程工艺进行分别制造,再通过先进封装技术将各个单元彼此互联,最终集成封装为一个系统级芯片组。

相比传统的SoC,Chiplet能够有效降低研发、设计与制造成本,并显著提升芯片良率。英特尔公司高级副总裁、中国区董事长王锐在2022世界集成电路大会上表示,Chiplet技术是产业链生产效率进一步优化的必然选择。“不但提高芯片制造良品率,利用最合适的工艺满足数字、模拟、射频、I/O等不同技术需求,而且更将大规模的SoC按照不同的功能,分解为模块化的芯粒,减少重复的设计和验证环节,大幅度降低设计复杂程度,提高产品迭代速度。且有利于后续的产品迭代,缩短上市周期。”

Chiplet的主要优势包括以下三种:

优势一:降低芯片设计的复杂程度,有效降低研发与设计成本。Chiplet芯粒设计灵活,且可重复使用,通过将已知的合格芯片裸片进行集成,能够缩短芯片的研发与设计周期,降低研发设计成本。据悉,设计28nm芯片的平均成本为4,000万美元,设计7nm芯片的成本上升至2.17亿美元。而The Linley Group的白皮书《Chiplets Gain Rapid Adoption: Why Big Chips Are Getting Small》中提出,Chiplet技术可以将大型7nm设计的成本降低25%。;

优势二:提升良率。SoC将多个不同类型计算任务的计算单元以光刻形式集成在同一片晶圆上,随着先进制程不断推进,单位面积上集成的晶体管数量越来越多,设计周期越来越厂,芯片面积也在加大。高性能计算等领域巨大运算需求推动逻辑芯片运算核心数量上升,配套SRAM容量、I/O数量随之提升。随着芯片面积的加大和集成的晶体管数量增多,对制造过程中的芯片良率提出较高挑战,让芯片生产中的工艺误差和加工缺陷显得愈发明显,一个微小的缺陷就可能导致整个大芯片报废。Chiplet技术将大芯片分割成不同功能模块进行独立制造,通过将广泛的、成熟的芯片裸片进行集成,只需保障各个被集成的成熟芯片良率即可,能够降低先进制程的研发与制造风险,有效提升良率。

优势三:大幅降低芯片制造成本。SoC中的逻辑计算单元对性能要求高,整体依赖先进制程,具有极高的生产壁垒与制造成本;Chiplet方案则可针对不同的模块采取不同的合适的制程,分开制造,最后采用先进封装技术进行组装,能大幅降低芯片的制造成本。

在多项优势的加持下,Chiplet技术已逐渐成为芯片厂商较为依赖的技术手段,被认为是未来芯片行业发展的重要方向。截至目前,芯原股份、长电科技、OPPO、阿里巴巴等众多国内知名企业已经开始研究Chiplet技术,共同构建Chiplet生态体系,助力行业快速发展。

国际半导体产业协会(SEMI)最新报告指出,生成式AI需求的爆发正推动全球芯片制造产能加速扩张。预计至2028年,全球12英寸晶圆月产能将达1,110万片,2024-2028年复合增长率达7%。其中,7nm及以下先进制程产能增速尤为显著,将从2024年的每月85万片增至2028年的140万片,年复合增长率14%(行业平均的2倍),占全球总产能比例提升至12.6%。

据供应链消息确认,高通新一代旗舰芯片骁龙8 Elite Gen 2(代号SM8850)将首次采用双轨代工策略:台积电负责基于N3P(3nm增强版)工艺的通用版本,供应主流安卓厂商;而三星则承接其2nm工艺(SF2)专属版本,专供2026年三星Galaxy S26系列旗舰机。此举标志着高通打破台积电独家代工依赖,三星先进制程首次打入头部客户供应链。

在AI算力需求爆发性增长的浪潮下,存储巨头美光科技交出超预期答卷。其2025财年第三季度营收达93亿美元,创历史新高,其中高带宽内存(HBM)业务以环比50%的增速成为核心引擎。凭借全球首款12层堆叠HBM3E的量产突破,美光不仅获得AMD、英伟达等头部客户订单,更计划在2025年末将HBM市占率提升至24%,直逼行业双寡头。随着下一代HBM4基于1β制程的性能优势验证完成,一场由技术迭代驱动的存储市场格局重构已然开启。

随着汽车智能化升级,高保真低延迟高集成度的音频系统成为智能座舱的核心需求。意法半导体(ST)推出的HFDA80D和HFDA90D车规级D类音频功放,以2MHz高频开关技术数字输入接口及先进诊断功能,为车载音频设计带来突破性解决方案。

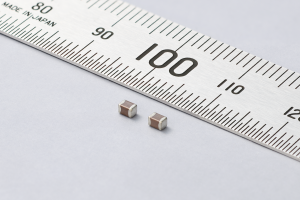

随着汽车智能化电动化进程加速,自动驾驶(AD)和高级驾驶辅助系统(ADAS)等关键技术模块已成为现代车辆标配。这些系统依赖于大量高性能电子控制单元(ECU)和传感器,导致车内电子元件数量激增。作为电路稳压滤波的核心元件,多层片式陶瓷电容器(MLCC)的需求随之水涨船高,尤其是在集成电路(IC)周边,对大容量电容的需求尤为迫切。然而,有限的电路板空间与日益增长的元件数量及性能要求形成了尖锐矛盾,元件的高性能化与小型化成为行业亟待攻克的关键难题。