发布时间:2021-11-29 阅读量:1368 来源: 亚德诺半导体 发布人: lina

问题:为什么使用DC-DC转换器应尽可能靠近负载的负载点(POL)电源?

答案:效率和精度是两大优势,但实现POL转换需要特别注意稳压器设计。

接近电源。这是提高电源轨的电压精度、效率和动态响应的最佳方法之一。负载点转换器是一种电源DC-DC转换器,放置在尽可能靠近负载的位置,以接近电源。因POL转换器受益的应用包括高性能CPU、SoC和FPGA——它们对功率级的要求都越来越高。例如,在汽车应用中,高级驾驶员辅助系统(ADAS)——例如雷达、激光雷达和视觉系统——中使用的传感器数量在稳步倍增,导致需要更快的数据处理(更多功耗)以最小的延迟检测和跟踪周围的物体。

在这些数字系统中,有很多都使用高电流和低电压,因此更需要尽可能缩短电源和负载之间的距离。高电流导致的一个明显问题是,从转换器到负载,线路产生的电压会不断下降。图1和图2显示了电源和负载之间引线电阻的最小化如何使转换器的输出电压降最小化——本例中是控制器IC和为CPU供电的MOSFET。

图1.PCB走线较窄情况下的DC-DC输出电压降

图2.PCB走线较宽情况下的DC-DC输出电压降

图2所示的较宽PCB走线减小了压降以达到精度要求,但还必须考虑寄生电感。图2中的PCB走线长度估计有约14.1 nh的电感,如图3的LTspice®模型所示。

图3.PCB走线电感的LTspice模型

电感会抑制电流的动态变化di/dt,当负载变化时,经过该寄生电感的电流受其时间常数限制,瞬态响应劣化。寄生电感导致的结果是电压下降,如图4中的仿真图所示。

图4.DC-DC输出电压突降和瞬态电流

将转换器放在负载附近可使PCB电阻和寄生电感的影响最小。DC-DC转换器IC应放置在最靠近CPU的位置。注意,图1和图2显示了传统高电流电源(即开关模式控制器和外部FET)的原理图。控制器FET解决方案可以处理上述应用所需的高电流负载。控制器解决方案的问题是外部FET有空间要求,因而可能难以获得真正的POL稳压器解决方案,如图5的示例布局所示。

图5.DC-DC转换器与CPU的理想布局

控制器的一个替代方案是单芯片解决方案,其中FET在转换器IC内部。例如,LTC3310S单片降压调节器(IC尺寸为3 mm×3 mm)可实现负载点解决方案,单个IC最多可提供10 A电流,并联多个IC可提供20 A电流。这些IC分别如图6和图12所示。

图6.LTC3310S降压调节器

图7.小尺寸LTC3310S支持POL布局

除了小封装尺寸外,LTC3310S还支持最大5 MHz的开关频率——高频工作可减小必要的输出电容和整体解决方案PCB尺寸。图8显示了LTC3310S的负载瞬态性能,其中8 A负载变化导致的输出电压偏移小于±40 mV,此性能的实现只需要110μF输出电容。

图8.LTC3310S的瞬态响应

尽管使用高功率单片POL转换器具有明显的优点,但有一个因素可能是搅局者:热量。如果转换器产生的热量过多,则它将无法用于已然很热的系统中。

在上述解决方案中,LTC3310S内部温度升幅通过高效率操作而得以最小化,即使在CPU、SoC和FPGA等高功耗器件周围的恶劣温度条件下,它也能够可靠地运行。此外,LTC3310S内置精密温度传感器,支持通过SSTT引脚测量内部结温,如图10所示,相应的温度传感器特性如图11所示。

图9.LTC3310S的热摄像头图像

图10.LTC3310S温度检测引脚

图11.软启动和温度监控操作

某些单片稳压器可通过多相并联操作扩展到更高负载应用。图12显示了多个LTC3310S器件并联并错相工作,使得电流能力加倍。

控制器的时钟由RT引脚上的单个电阻设置,子节点的相对相位通过RT引脚上的电阻分压器编程。在图12所示的情况中,RT接地,将子节点设置为相对于控制器相移180°。

图13显示了2通道转换器的电感电流和输出纹波电流,如图12所示。同相性能与双反相性能进行比较。反相操作将输出纹波电流(通过抵消)从14 A峰峰值(单相)降低到6 A峰峰值(双相),而无需额外的外部滤波器。

结论

总之,LTC3310S是一款高效且小型的POL解决方案,适用于为高耗电CPU、SoC、FPGA供电的高电流电源系统。其尺寸很小,并可优化功率效率,导致自发热很低,因而其可以非常靠近负载。它可以轻松并联,在多相解决方案中使用多个LTC3310S可提高功率。

图12.20 A双相单片稳压器POL解决方案

图13.比较两个版本的双通道转换器的电感电流和输出电流:(a) 同相通道与 (b) 反相通道

(来源:亚德诺半导体,作者:Atsuhiko Furukawa)

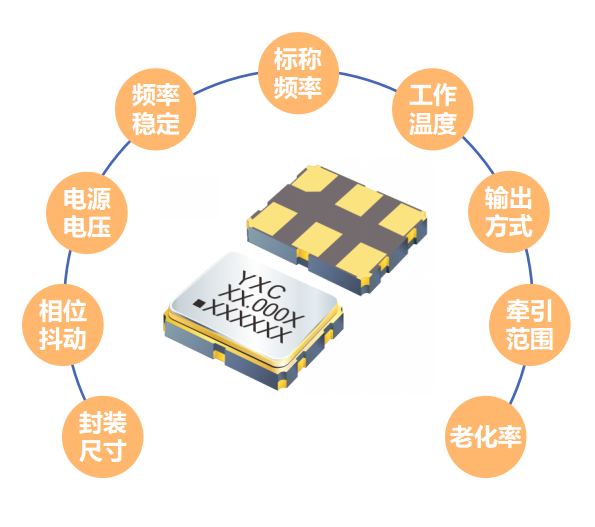

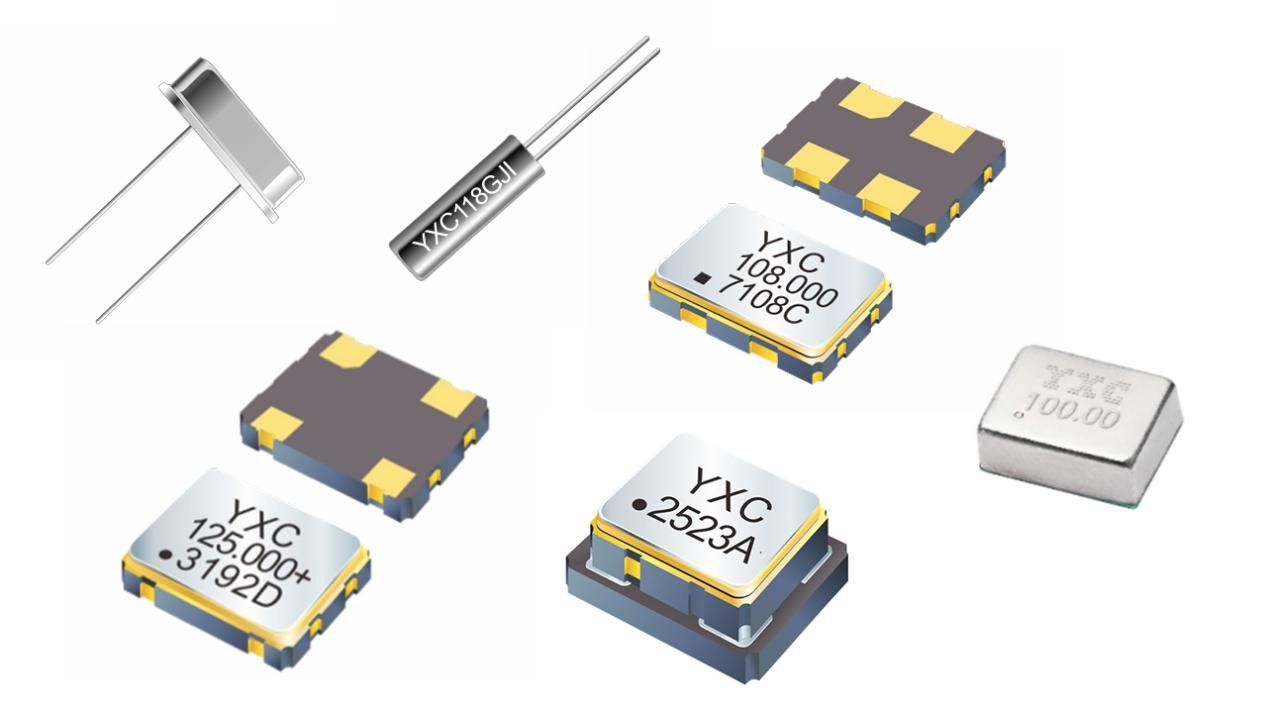

在汽车电子智能化、网联化与电动化深度融合的浪潮中,车载时钟系统的精度与可靠性正成为决定整车性能的核心命脉。作为电子架构的"精准心跳之源",车规级晶振的选型直接影响ADAS感知、实时通信、动力控制等关键功能的稳定性。面对严苛路况、极端温差及十年以上的生命周期挑战,工程师亟需兼具高稳定性与强抗干扰能力的时钟解决方案——小扬科技将聚焦车规级晶体/晶振核心参数,3分钟助您精准锁定最优型号。

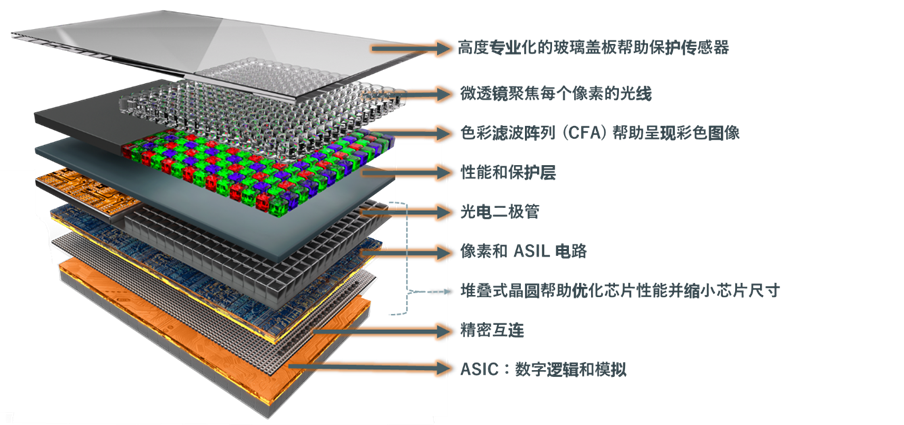

在技术创新的浪潮中,图像传感器的选型是设计与开发各类设备(涵盖专业与家庭安防系统、机器人、条码扫描仪、工厂自动化、设备检测、汽车等)过程中的关键环节。选择最适配的图像传感器需要对众多标准进行复杂的综合评估,每个标准都直接影响最终产品的性能和功能。从光学格式(Optical Format)和动态范围(Dynamic Range),到色彩滤波阵列(CFA)、像素类型、功耗及特性集成,这些考量因素多样且相互交织、错综复杂。

压控晶振(VCXO)作为频率调控的核心器件,已从基础时钟源升级为智能系统的"频率舵手"。通过变容二极管与石英晶体的精密耦合,实现电压-频率的线性转换,其相位噪声控制突破-160dBc/Hz@1kHz,抖动进入亚纳秒时代(0.15ps)。在5G-A/6G预研、224G光通信及自动驾驶多传感器同步场景中,VCXO正经历微型化(2016封装)、多协议兼容(LVDS/HCSL/CML集成)及温漂补偿算法的三重技术迭代。

在电子设备的精密计时体系中,晶体振荡器与实时时钟芯片如同时间系统的"心脏"与"大脑":晶振通过石英晶体的压电效应产生基础频率脉冲,为系统注入精准的"生命节拍";而实时时钟芯片则承担时序调度中枢的角色,将原始频率转化为可追踪的年月日时分秒,并实现闹钟、断电计时等高级功能。二者协同构建现代电子设备的"时间维度"。

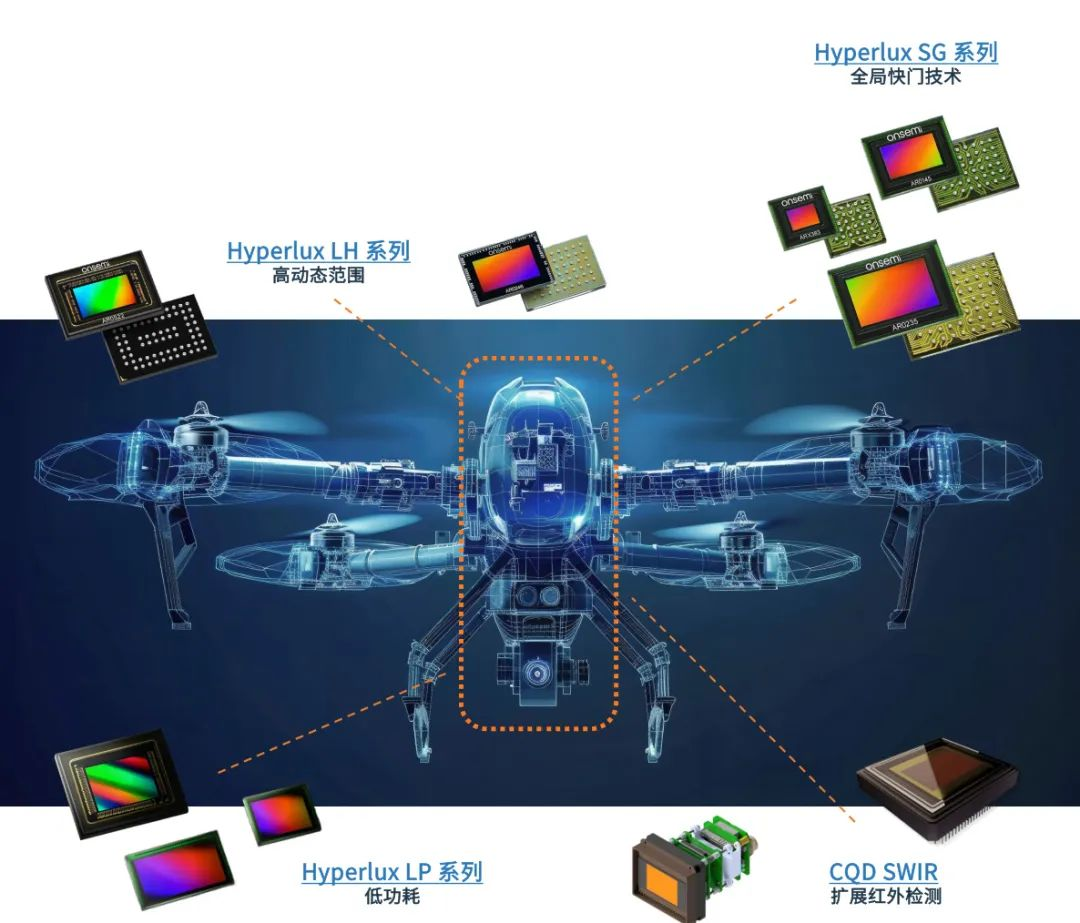

无人机已不再是简单的飞行器,而是集成了尖端感知与决策能力的空中智能载体。其核心系统——特别是自主导航与感知技术——是实现其在测绘、巡检、农业、物流、安防等多个领域高效、精准作业的关键。本文将深入剖析无人机如何通过这些核心技术“看见”、“思考”并“规划”路径,实现真正意义上的自主飞行能力。