发布时间:2021-11-29 阅读量:1044 来源: 我爱方案网 作者: 亚德诺半导体

为了节省成本,另一种方法是使用单个5V 电源设计架构。单个5V电源轨显著降低了模拟前端隔离电源设计的复杂性。但它会引入其他痛点,可能降低测量解决方案的精度。AD4111 进行了电压和电流测量所需的大量整合工作,并解决了5V 电源解决方案的局限性。

图1. AD4111功能框图。

集成前端

AD4111是一款24位∑-Δ型ADC,通过实现创新而简单的信号链,缩短了开发时间,降低了设计成本。它利用ADI的专有iPassives™技术,将模拟前端和ADC融合在一起。这使得 AD4111 能够接受 ±10 V 电压输入和 0 mA 至 20 mA 电流输入,同时无需外部组件即可在单个 5V 或 3.3V 电源下工作。电压输入指定为 ±20V 的超量程,在此范围内,该器件仍可在电压引脚上提供有效转换和 ±50V 的绝对最大规格。电流输入指定为 -0.5 mA 至 24 mA 的范围,可实现接近0 mA的准确电流测量,提供精确的24 mA转换。

AD4111

●根据以下标准进行鲁棒性测试:IEC6100-4-2、IEC6100-4-3、

●IEC6100-4-4、IEC6100-4-5、IEC6100-4-6、CISPR 11

●集成模拟前端的 24 位 ADC

●快速灵活的输出速率:1.25 SPS 至 31.25 kSPS

●每通道通道扫描速率:6.21 kSPS(161 μs 建立时间)

●1 kSPS 时每个通道 16 个无噪声位

●20 SPS 时每个通道的 50 Hz 和 60 Hz 抑制为 85 dB

●±10 V 输入,4 个差分或 8 个单端

●引脚绝对最大额定值:±50 V

●高达 ±20 V 的超量程

●≥1 MΩ 阻抗

●25°C 时精度为 ±0.06%

●开路检测

●0 mA 至 20 mA 输入,4 个单端

●引脚绝对最大额定值:±50 mA

●高达 −0.5 mA 至 +24 mA 的超量程

●60 Ω 阻抗

●25°C 时精度为 ±0.08%

●片内 2.5 V 基准电压源

●25°C 时精度为 ±0.12%,漂移为 ±5 ppm/°C(典型值)

●内部或外部时钟

●电源

●AVDD = 3.0 V 至 5.5 V

●IOVDD = 2 V 至 5.5 V

●总 IDD = 3.9 mA

●温度范围:−40°C 至 +105°C

●3 线或 4 线串行数字接口(SCLK 上的施密特触发器)

●SPI、QSPI、MICROWIRE 和 DSP 兼容

AD4111的电压输入保证最小阻抗为1MΩ。这样可以去除±15 V外 部缓冲器,进一步节省电路板空间和BOM成本。5 V 设计要求每个电压输入必须有一个高阻抗分压器,这会占用电路板空间。离散解决方案的设计需要权衡精密电阻的成本与精度。为了解决这个问题,AD4111在每个输入端采用了一个高阻抗精密分压器,如图3所示。

开路检测

通常,单个5 V 设计的限制是缺少开路检测,一般是对15 V 电源轨使用高阻抗电阻,将开路连接拉至超出范围的电压。AD4111 采用5 V 或3.3V 电源提供独特开路检测功能,克服了这一问题。此方法将开路检测与超出范围的故障分开,进一步简化了诊断。通过在AD4111内部包含此功能,前端无需上拉电阻,因此也无需15 V电源,如图2所示。消除±15 V 电源减少了隔离电路的复杂性、面积和辐射。对于不需要开路检测的应用,可以使用另一种通用的AD4112。该器件具有AD4111的所有优点,但没有开路检测。

图2. 典型高端解决方案。

系统级解决方案

AD4111 集成了基准电压和内部时钟,有助于进一步减小电路板尺寸并降低BOM成本,同时允许使用外部组件,应付需要更高精度和更低温度误差转换的情况。图2和图3分别显示了典型的高端和低端解决方案。图2和图3中突出显示了可完全被AD4111 取代的信号链的比例。AD4111的总不可调整误差(TUE)精度规范旨在达到系统级要求。对于许多解决方案,精度可能足以省略任何额外校准。在现有的高精度解决方案中,通常按通道对模块进行校准。AD4111 采用高匹配输入设计,因此校准一个输入便可所有输入上提供类似的精度。

图3. 典型低端解决方案。

EMC测试

PLC 和 DCS 模块通常在恶劣的工业环境中运行,并且必须承受电磁干扰(EMI)的情况。在设计具有电磁兼容性(EMC)功能的输入模块时,这会增加复杂性,因为大多数设备的额定值不适用于EMC,因此设计输入保护和滤波电路就变得复杂起来。这可能显著增加设计和测试开发时间。EMC 实验室租金昂贵,测试失败可能意味着长时间延迟,直到电路板可以重新设计和重新测试。

AD4111 已经被设计成了一个印刷电路板(PCB),演示了一个经过验证的EMC解决方案。该电路板的特点是确保电路性能不会受到辐射射频(RF)或传导RF干扰的永久影响,并且已被证明具有足够的抗静电放电(ESD)、电快速瞬变(EFT)和浪涌的能力,符合IEC 61000-4-x 标准集。该电路板还针对 CISPR 11 进行了评估,其辐射发射水平远低于A类限值。

结论

AD4111是一款高度集成的系统级ADC,具有全面的可配置性。它能够接受±10 V电压输入和0 mA 至20 mA 电流输入,采用5 V 或3.3V 单电源供电,具有开路检测功能和许多其他功能,为模拟输入模块设计提供独特的解决方案。它采用6 mm × 6 mm、40 引脚 LFCS P封装,之前需要完整复杂PCB的模块现在可由单个器件替代。

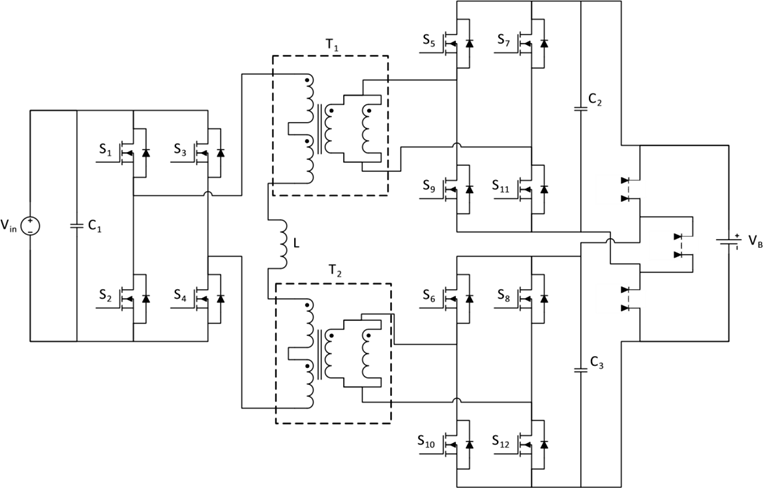

碳化硅(SiC)功率器件正以颠覆性优势引领工业充电器变革——其超快开关速度与超低损耗特性,驱动功率密度实现跨越式提升,同时解锁了传统IGBT无法企及的新型拓扑架构。面对工业应用对高效隔离式DC-DC转换的严苛需求,本文将深入解析从600W至深入解析从600W至30kW全功率段的拓扑选型策略,揭示SiC技术如何成为高功率密度设计的核心引擎。

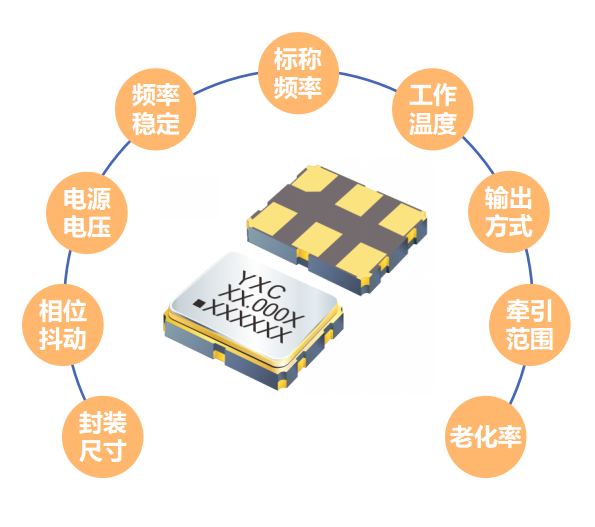

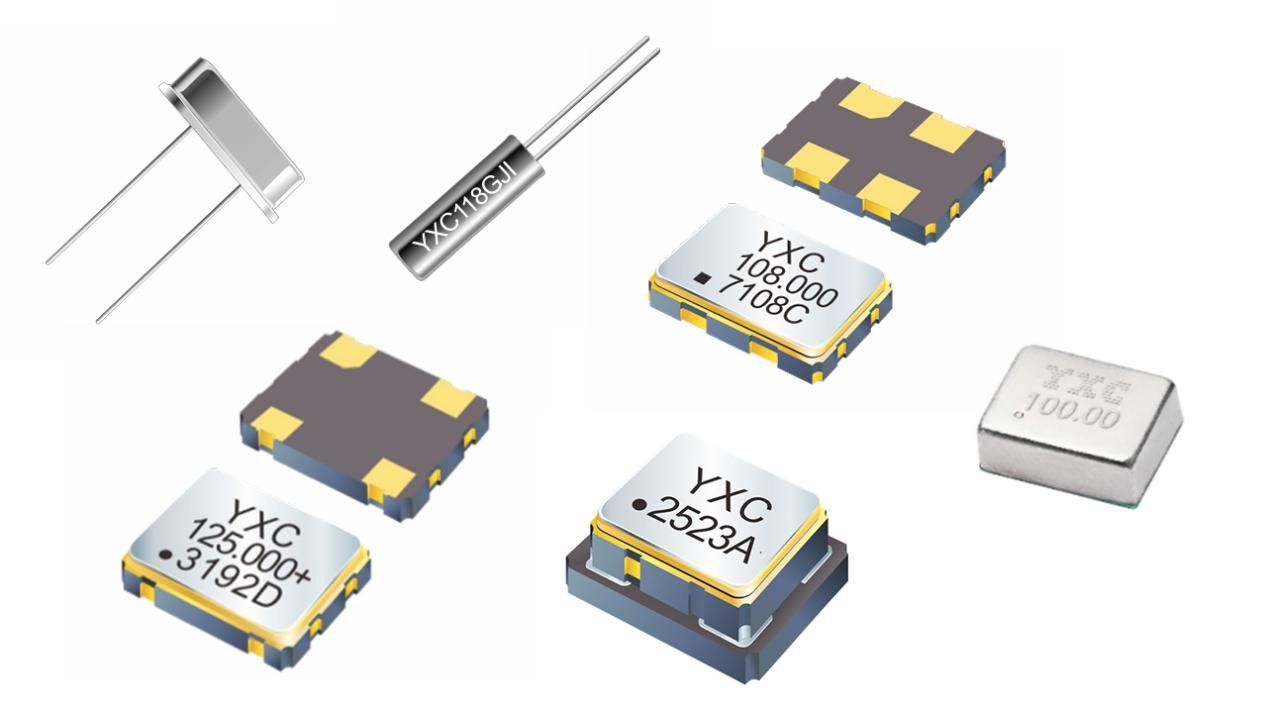

在汽车电子智能化、网联化与电动化深度融合的浪潮中,车载时钟系统的精度与可靠性正成为决定整车性能的核心命脉。作为电子架构的"精准心跳之源",车规级晶振的选型直接影响ADAS感知、实时通信、动力控制等关键功能的稳定性。面对严苛路况、极端温差及十年以上的生命周期挑战,工程师亟需兼具高稳定性与强抗干扰能力的时钟解决方案——小扬科技将聚焦车规级晶体/晶振核心参数,3分钟助您精准锁定最优型号。

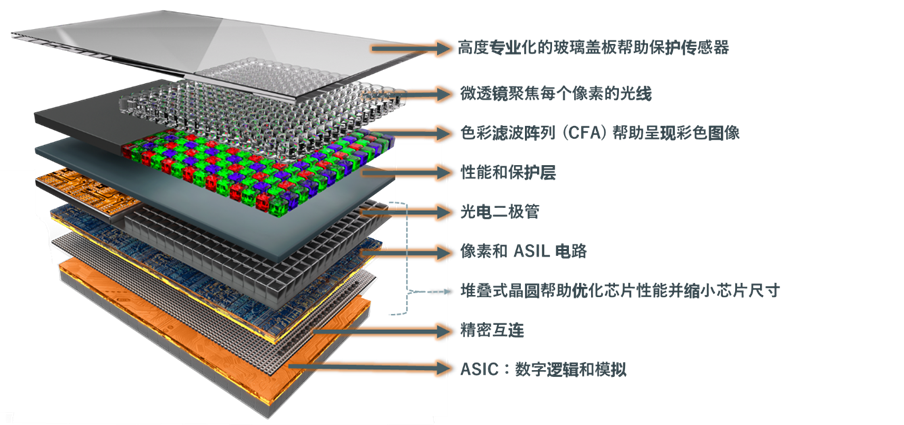

在技术创新的浪潮中,图像传感器的选型是设计与开发各类设备(涵盖专业与家庭安防系统、机器人、条码扫描仪、工厂自动化、设备检测、汽车等)过程中的关键环节。选择最适配的图像传感器需要对众多标准进行复杂的综合评估,每个标准都直接影响最终产品的性能和功能。从光学格式(Optical Format)和动态范围(Dynamic Range),到色彩滤波阵列(CFA)、像素类型、功耗及特性集成,这些考量因素多样且相互交织、错综复杂。

压控晶振(VCXO)作为频率调控的核心器件,已从基础时钟源升级为智能系统的"频率舵手"。通过变容二极管与石英晶体的精密耦合,实现电压-频率的线性转换,其相位噪声控制突破-160dBc/Hz@1kHz,抖动进入亚纳秒时代(0.15ps)。在5G-A/6G预研、224G光通信及自动驾驶多传感器同步场景中,VCXO正经历微型化(2016封装)、多协议兼容(LVDS/HCSL/CML集成)及温漂补偿算法的三重技术迭代。

在电子设备的精密计时体系中,晶体振荡器与实时时钟芯片如同时间系统的"心脏"与"大脑":晶振通过石英晶体的压电效应产生基础频率脉冲,为系统注入精准的"生命节拍";而实时时钟芯片则承担时序调度中枢的角色,将原始频率转化为可追踪的年月日时分秒,并实现闹钟、断电计时等高级功能。二者协同构建现代电子设备的"时间维度"。