发布时间:2021-01-15 阅读量:1651 来源: 我爱方案网 作者: 雕塑者

在LDO应用中,会有一个输入输出压差范围的概念,如AMS1117,压差Dropout Voltage的典型值为1.1V,即:输入至少比输出高1.1V的压降才能支持所需要的输出。

在之前写过的一篇文章《LDO与DC-DC 的入门理解》中,我们可以了解到LDO是靠内部电路分压达到降压输出,而DC-DC则是通过“断续的供给”达到降压输出。那么,DC-DC降压电路输入和输出是否需要压差呢?思考一个场景:某款Buck芯片自身工作电压范围为2.7-5.5V,现需要该芯片输出3.3V/2A。当正常输入5V时,该芯片可满载输出3.3V,当输入电压只有3.5V时,该芯片是否还能正常输出3.3V/2A呢?

该问题本质其实是DC-DC降压电路中,在输入输出规格内,芯片占空比是否受限、导通损耗的问题。理论上,但芯片的开关周期达到100%时,DC-DC其实是一个“直通”状态,即输出电压等于输入电压,当然,真实的应用中,芯片的占空比不会达到完整的100%,而且由于芯片里集成或外置的MOSFET的导通内阻以及输出电感上Rdc,实际输出电压与输入电压之间会有一个压差。

以JW5092为例,输入4.7V时,可输出3.3V/2A,但当输入为4.0V的时候,是否还能满载输出?

首先,根据能量守恒,我们可知(Vin-Vout)*ton=Vout*toff,由此

Vout = Vin * D,D为开关周期中,“开”的占空比。

考虑,MOS管导通内阻Rds、电感内阻RL,可得:

Vout = Vin * D- Iout x (Rds(ON) + RL)

查看规格书——

当Vin = 4V时,若输出2A,暂时忽略电感选型上的内阻差异,则:

由此可知,此时该当输入为4.0V的时候,JW5092无法满载输出3.3V/2A

所以DC-DC降压电路中,实际输出电压要等于输入电压减去Buck芯片里集成或外置的MOSFET的Rds(on)以及输出电感的Rdc上产生的压降,包括由于占空比受限导致的无法满载输出。带载越重,输出电压越低。当你的输入输出压差范围很小,但仍然需要满载输出时,请考虑号称可达100%占空比的芯片!

作者介绍:雕塑者(笔名),一名乐于开源文化的工程师,个人公众号【硬件大熊】。后续原创技术应用笔记还将在我爱方案网上线,敬请期待!

来源:我爱方案网

版权声明:本文为博主原创,未经本人允许,禁止转载!

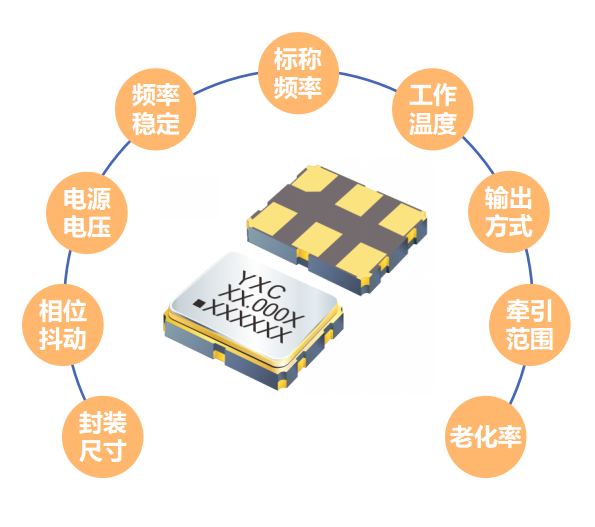

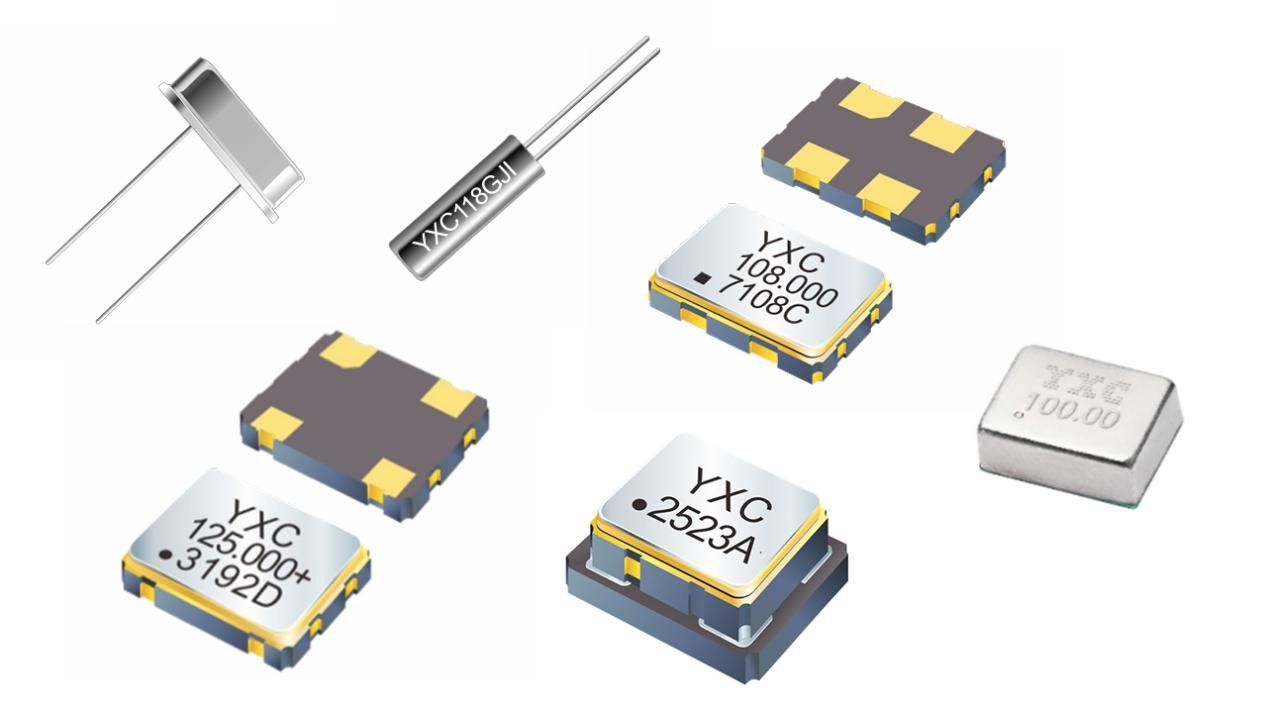

在汽车电子智能化、网联化与电动化深度融合的浪潮中,车载时钟系统的精度与可靠性正成为决定整车性能的核心命脉。作为电子架构的"精准心跳之源",车规级晶振的选型直接影响ADAS感知、实时通信、动力控制等关键功能的稳定性。面对严苛路况、极端温差及十年以上的生命周期挑战,工程师亟需兼具高稳定性与强抗干扰能力的时钟解决方案——小扬科技将聚焦车规级晶体/晶振核心参数,3分钟助您精准锁定最优型号。

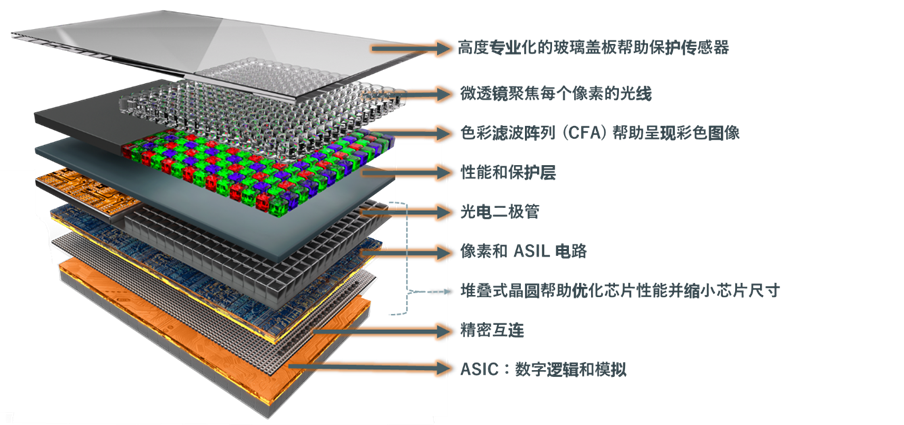

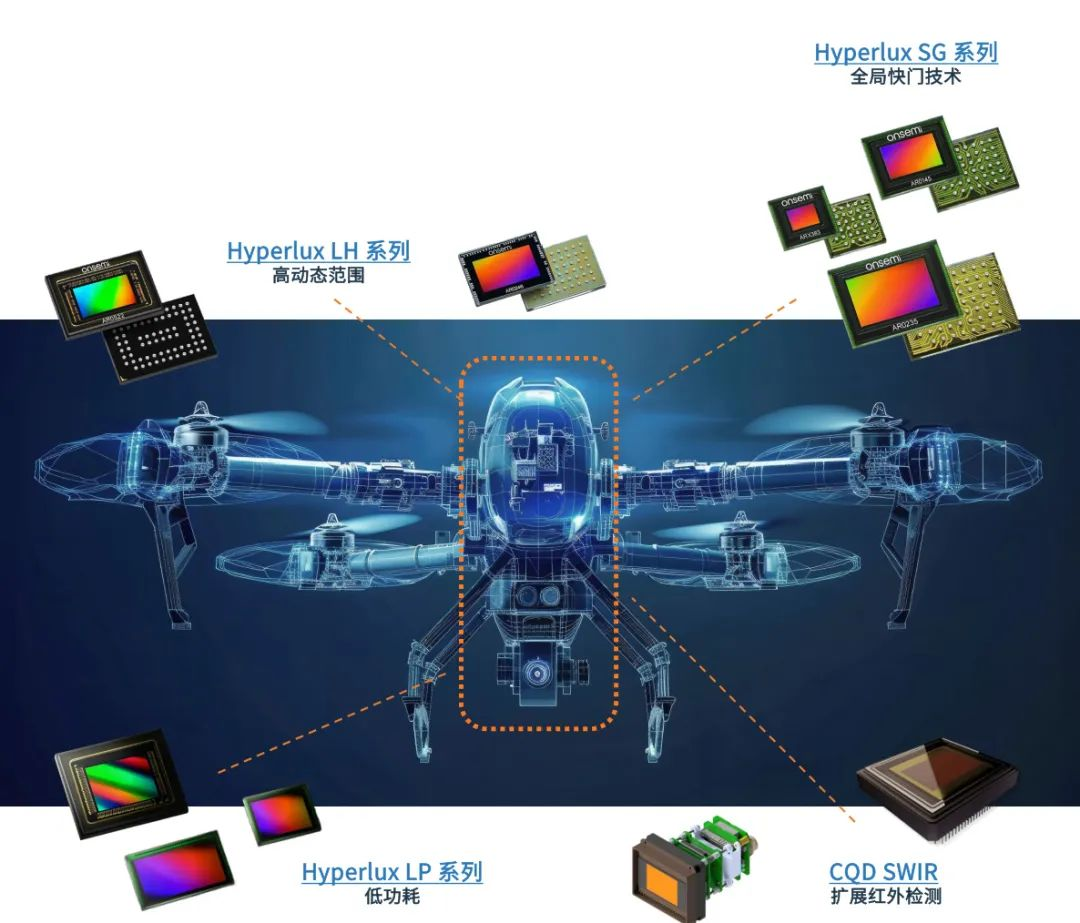

在技术创新的浪潮中,图像传感器的选型是设计与开发各类设备(涵盖专业与家庭安防系统、机器人、条码扫描仪、工厂自动化、设备检测、汽车等)过程中的关键环节。选择最适配的图像传感器需要对众多标准进行复杂的综合评估,每个标准都直接影响最终产品的性能和功能。从光学格式(Optical Format)和动态范围(Dynamic Range),到色彩滤波阵列(CFA)、像素类型、功耗及特性集成,这些考量因素多样且相互交织、错综复杂。

压控晶振(VCXO)作为频率调控的核心器件,已从基础时钟源升级为智能系统的"频率舵手"。通过变容二极管与石英晶体的精密耦合,实现电压-频率的线性转换,其相位噪声控制突破-160dBc/Hz@1kHz,抖动进入亚纳秒时代(0.15ps)。在5G-A/6G预研、224G光通信及自动驾驶多传感器同步场景中,VCXO正经历微型化(2016封装)、多协议兼容(LVDS/HCSL/CML集成)及温漂补偿算法的三重技术迭代。

在电子设备的精密计时体系中,晶体振荡器与实时时钟芯片如同时间系统的"心脏"与"大脑":晶振通过石英晶体的压电效应产生基础频率脉冲,为系统注入精准的"生命节拍";而实时时钟芯片则承担时序调度中枢的角色,将原始频率转化为可追踪的年月日时分秒,并实现闹钟、断电计时等高级功能。二者协同构建现代电子设备的"时间维度"。

无人机已不再是简单的飞行器,而是集成了尖端感知与决策能力的空中智能载体。其核心系统——特别是自主导航与感知技术——是实现其在测绘、巡检、农业、物流、安防等多个领域高效、精准作业的关键。本文将深入剖析无人机如何通过这些核心技术“看见”、“思考”并“规划”路径,实现真正意义上的自主飞行能力。