发布时间:2019-11-4 阅读量:662 来源: 发布人: CiCi

11 月 4 日讯,晶圆代工龙头台积电 2 日庆祝创立 33 周年,并举行员工运动会,台积电创办人张忠谋也在退休后携夫人张淑芬首次回来参加。

庆典上,董事长、联席 CEO 刘德音谈到了台积电的先进工艺规划,最先进的 2nm 工艺也进入了先导规划中,明年则会量产 5nm 工艺。

2019 年是半导体产业遇逆风的一年,全球半导体产业将衰退 12%。而半导体除记忆体之外,也预估将衰退 3%。不过,台积电确定 2019 年将较 2018 年小幅成长,这样的成长虽然不够多,但也是一个逆势成长。

所以,台积电的表现算是突出。而对于 2020 年的展望,台积电也已经做好准备,借由大规模的产能投资布建,预期将会是一个大大成长的年。

根据台积电的规划,2nm 工艺是一个重要节点,Metal Track ( 金属单元高度 ) 和 3nm 一样维持在 5x,同时 Gate Pitch ( 晶体管栅极间距 ) 缩小到 30nm,Metal Pitch ( 金属间距 ) 缩小到 20nm,相比于 3nm 都小了 23%。

此外,台积电在台中的晶圆 15 厂,目前借由 N7 制程已经进行了 2 年独步全球的快速 Ramp-out 和大量制造,使得在其 N7 的学习取线上,已经产出了超过 100 万片的 12 吋晶圆。而首次使用 EUV 技术的 N7+ 制程也已经于 2019 年 6 月份开始大量生产,并且有良好的良率表现。

至于,最新进的 N5 制程即将准备就绪。而且,在过去的一年中,在新竹的晶圆 12 厂及在台南的 18 厂,都有缴出很好的成绩,客户也都十分的满意。2020 年台积电的 N5 将接续 N7 的脚步,缔造又一个世界最先进半导体技术的里程碑。

此外,借助公司成立 33 周年的契机,台积电也宣布了新的福利,凡是 2019 年 5 月 31 日以前到职,职级 60 到 64 的直接人员,职级 20 到 26 的行政及技术人员,以及职级 31 到 33 的工程师与管理师,总计约有 39000 名同仁,台积电将在 12 月发给每人新台币 12000 元(约合 2774 元人民币)的红包,总计将发出 4.68 亿元的红包奖金。

佰维存储2025年上半年实现营业收入3,912,336,913.69元,同比增长13.7%。但受行业周期等因素影响,公司报告期内归属于上市公司股东的净亏损为225,795,502.52元,同比由盈转亏;扣除非经常性损益后的净亏损为231,666,270.28元,同样出现同比下滑。业绩压力主要源于行业价格波动及公司战略性投入增加。

2025年上半年,工业富联(股票代码:601138.SH)实现营业收入3607.6亿元,同比大幅增长35.58%;归属于上市公司股东的净利润达121.13亿元,同比增长38.61%;扣非净利润116.68亿元,同比增长36.73%,核心财务指标均创历史新高。报告期内,公司总资产规模增至3831.28亿元,同比增长20.66%,展现出强劲的资产扩张能力。

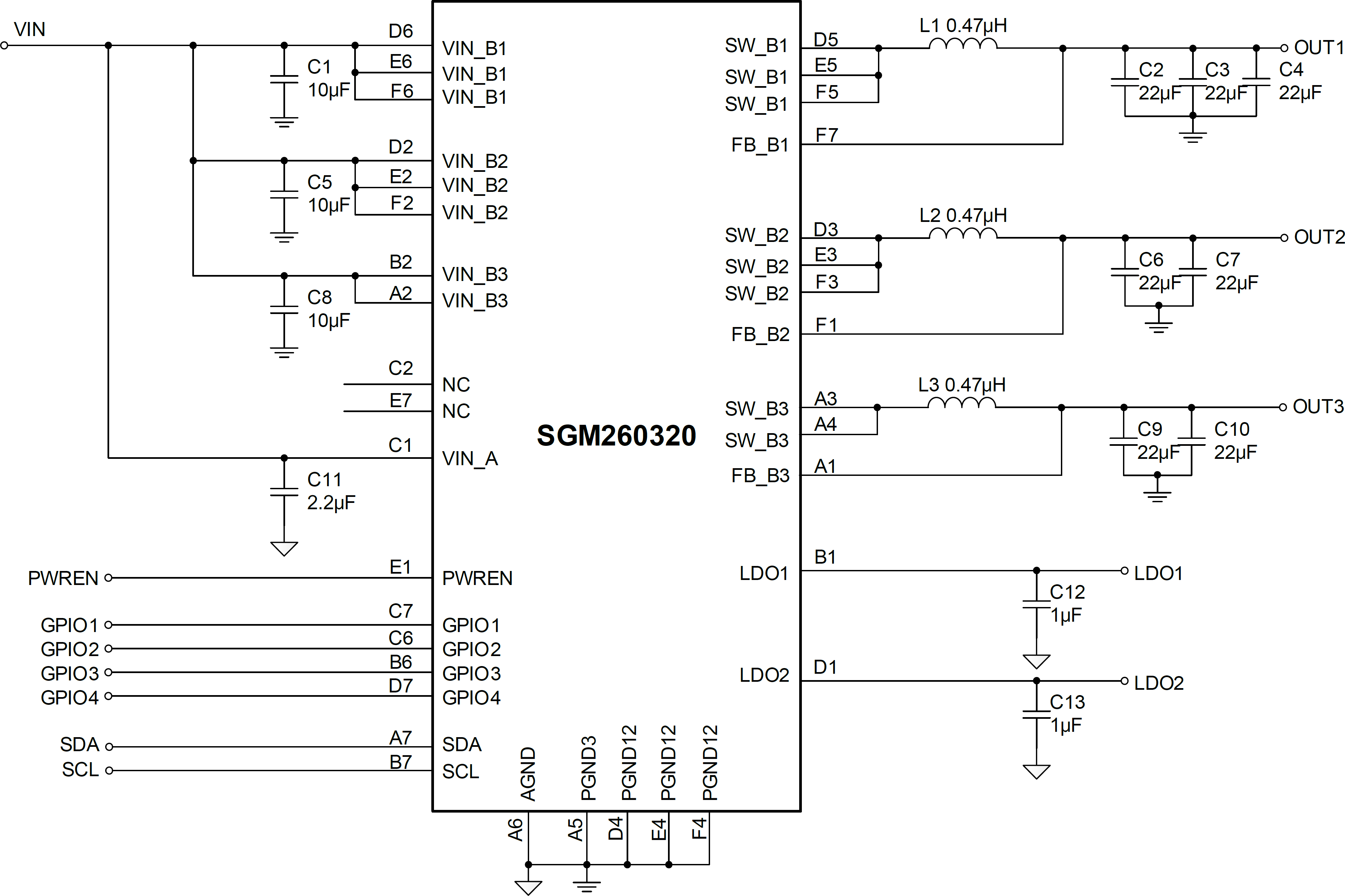

在追求电子设备小型化、高性能和超低功耗的时代,复杂的多轨电源设计已成为研发的关键挑战。传统分立式电源方案不仅占用宝贵的PCB面积,也增加了设计难度与系统功耗控制的复杂性。固态硬盘(SSD)、现场可编程门阵列(FPGA)、微控制器单元(MCU)系统及便携设备对电源管理集成电路(PMIC)的要求日益严苛:高效转换、低待机功耗、高集成度、精确调压以及智能化管理缺一不可。圣邦微电子(SG Micro)推出的SGM260320 PMIC,正是瞄准这一市场需求,以高度集成、卓越性能和丰富的可配置功能,提供了一站式的高效供电解决方案。

随着智能手机影像功能逐渐成为用户核心需求,光学防抖(OIS)技术正面临前所未有的性能挑战。TDK株式会社凭借旗下InvenSense公司15年OIS/EIS技术积累,最新推出的SmartMotion® ICM-536xx系列六轴IMU,正在打破高端防抖技术的成本壁垒。该方案通过突破性的6.4kHz输出数据速率和20位分辨率,首次将专业级防抖性能引入主流移动设备市场。

2024年,全球工业机器人市场经历了一次明显的周期性调整。国际机器人联合会(IFR)的初步统计数据显示,全年新装机量约为52.3万台,较上年下滑约3%。这是近年来该市场罕见出现的负增长,反映出多重经济与技术周期叠加下的复杂局面。