发布时间:2018-05-11 阅读量:821 来源: 我爱方案网 作者: Miya编辑

全球第一大芯片自动化设计解决方案提供商及全球第一大芯片接口IP供应商、信息安全和软件质量的全球领导者Synopsys近日宣布与TSMC合作,共同为TSMC 22nm超低功耗(ULP)与22nm超低漏电(ULL)平台开发DesignWare® 基础IP。该基础IP包含用于TSMC 22nm工艺的逻辑库、嵌入式内存以及一次性可编程(one-time programmable,OTP)非挥发性内存(non-volatile memories,NVM),能协助设计人员大幅降低功耗,同时满足各式应用的性能需求。DesignWare Duet Package包括了具备面积优化的高速低功耗嵌入式内存、使用标准核心氧化物(core oxide)或厚IO 氧化物以实现低漏电率的逻辑库、内存测试与修复能力以及功耗优化套件,能为SoC带来最佳的结果质量。

DesignWare HPC设计套件内容包括高速、高密度的内存实例(memory instance)和逻辑单元,能协助SoC设计人员进行CPU、GPU与DSP核心的优化,以达到速度、面积与功耗的最佳平衡。用于TSMC 22nm ULP与22nm ULL工艺的DesignWare OTP NVM IP无须额外的光罩层数或制程步骤,且能以最少的硅足迹(footprint)达到高产出、高安全性及高可靠性。

TSMC设计基础架构营销事业部资深处长Suk Lee表示:“TSMC与Synopsys多年成功的合作经验有助于双方客户实现SoC在性能、功耗及芯片面积的目标。通过为TSMC 22nm ULP与22nm ULL工艺提供DesignWare 基础IP,Synopsys作为业界领导厂商,持续提供通过验证的IP解决方案,协助设计人员减少设计工作量,同时在TSMC最新技术中实现设计目标。”

要点:

●基于TSMC 22nm ULP与22nm ULL平台的DesignWare Duet Package,包含实现完整SoC所需的所有基础IP,包括逻辑库、memory compilers与power optimization kits等。

●基于TSMC 22nm ULP工艺的DesignWare 高性能(HPC)设计能为CPU、GPU及DSP处理器核心提升其时序性能、功耗及芯片面积等表现。

●针对校正(calibration)、加密钥(encryption keys)及安全码储存等应用,基于TSMC 22nm ULP及22nm ULL的DesignWare OTP NVM IP,不需要额外的光罩层数(mask layer)或制程步骤(process step),就能支持1Mb 实例(instance)。

美国为防止高端人工智能(AI)芯片通过第三方渠道流入中国,已秘密要求芯片制造商英伟达(NVIDIA)、超威半导体(AMD)等企业在出口至部分国家的AI芯片中植入追踪程序,以便实时监控芯片流向

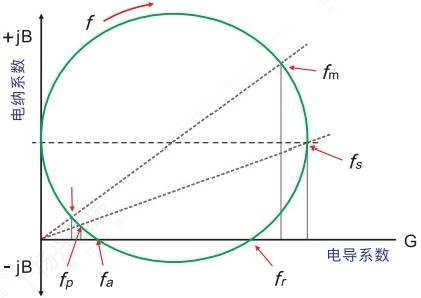

在电子电路设计中,晶振的每一项参数都与产品命运息息相关——哪怕只差0.1ppm,也可能让整板“翻车”。看似最基础的术语,正是硬件工程师每天必须跨越的隐形门槛。

在电子电路设计中,晶振的每一项参数都与产品命运息息相关——哪怕只差0.1ppm,也可能让整板“翻车”。看似最基础的术语,正是硬件工程师每天必须跨越的隐形门槛。

电路板中常用到恒温与温补这两种晶振,恒温晶振与温补晶振都属于晶体振荡器,既有源晶振,所以组成的振荡电路都需要电源加入才能工作

汽车电子系统日益复杂,尤其在48V架构、ADAS与电控系统普及的当下,对瞬态电压抑制器(TVS)的功率密度、高温耐受性及小型化提出了严苛挑战。传统大功率TVS往往体积庞大,难以适应紧凑的ECU布局。威世科技(Vishay)日前推出的T15BxxA/T15BxxCA系列PAR® TVS,以创新封装与卓越性能直面行业痛点,为下一代汽车设计注入强大保护能力。