【导读】随着芯片尺寸的缩小,最直接影响到的就是固晶制程的难易度;同时芯片上的电极必须跟着变小,使用的键合线的线径也必须减小,所搭配的瓷嘴也必须同步优化。那么,进入了”小芯片封装”的领域之后,首先要克服的是哪些问题呢?

近年来,随着LED芯片材料的发展,以及取光结构、封装技术的优化,单芯片尺寸的功率(W)越做越高,芯片的光效(lm/W)、性价比(lm/$)也越来越好,在这样的背景支持之下,LED芯片的微小化已成趋势。芯片尺寸微小化背后的含意,除了发光组件的总体尺寸能更佳符合未来产品轻、薄、短、小的趋势之外,单一外延片所能切割的小芯片数量更多了,固定功率下所需使用的芯片数量更少了,这些对于降低LED的生产支出有很大的帮助,毕竟”成本”永远都是个大问题。

在大功率照明领域,采用多个小芯片串并联的技术已经使用的很成熟也很广泛。和单一大功率芯片比起来,此工艺的芯片成本较低,整体的散热性也更好、光效更高、光衰更慢,可同时达到高效率及高功率的目标,虽然有工序较复杂、信赖性较低等隐忧,但也难以动摇它的地位。其次,在显示屏应用的领域,RGB多芯片封装是一个主流的工艺,随着象素的密度越高(即分辨率越高),单位面积下单个象素点的尺寸就必须越来越小,在逐渐朝着”小间距化”方向发展的同时,所能使用的R、G、B叁色芯片的尺寸也必须越来越小,藉此满足市场上高分辨率的要求。从上述趋势看来,如何做好小尺寸芯片的封装,就成为一个重要的课题。

在LED封装的技术中,目前仍是以传统固晶、打线的制程为主,至于时下当红的覆晶封装(Flip Chip)或是芯片级封装(Chip Scale Package,CSP)等其他新制程,碍于当前良率、成本、设备投资等考虑,短时间内还是很难取代塬有制程。随着芯片尺寸的缩小,最直接影响到的就是固晶制程的难易度;同时芯片上的电极必须跟着变小,使用的键合线的线径也必须减小,所搭配的瓷嘴也必须同步优化。因此,进入了”小芯片封装”的领域之后,首先要克服的难点就是固晶、打线制程会用到的固晶胶、键合线、瓷嘴。

关于固晶的挑战

固晶胶是固晶制程的关键耗材,它的作用包含了固定芯片、(导电)及散热,其主要成分由高分子或是银粉加高分子材料所组成。藉由成分配比的不同,形成了不同的剪切强度、触变指数、玻璃转移温度、体积电阻率等等的特性参数,进而达到了不同的固晶效果及信赖性。此外,随着芯片尺寸的缩小,固晶胶的使用量也必须减小,如果胶量过多容易产生芯片滑动,若是过少又可能导致芯片因粘不紧而掉落,这其中该如何拿捏也是一门艺术了。

如何选用键合线材

所谓好的键合线材,必须具备以下要求:

1.满足客户规范的机械及电气性能(如融断电流、弧长弧高、球形尺寸等)

2.精确的直径

3.表面无划痕、清洁无污染

4.无弯曲、扭曲应力

5.内部组织结构均匀

除了上述要求之外,小线径线材又可能面临多芯片间串并联,或是植球型焊线如BSOB(Bond Stick On Ball)、BBOS(Bond Ball On Stitch)等特殊打线手法的需求,更是制线工艺上的挑战,举例来说,芯片串联的过程会涉及到芯片间Pad to Pad的打线,若是使用铜线或纯银线来进行焊接会有作业性不好及良率不高的问题,远远不及纯金及高金、合金线的表现,这些都是要纳入考虑的。

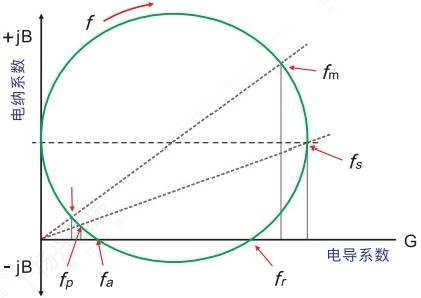

此外,随着线径变小,键合线的荷重(Breaking load,BL)会跟着下降,将影响到焊线的拉力与信赖性;再来,随着各种线材的成分配比、合金的均匀控制,以及拉丝、煺火条件的不同,将产生不同的线材硬度、荷重、延伸率(Elongation,EL)、热影响区(Heat Affection Zone,HAZ)及电阻等特性,在焊线变细的同时如何能抵抗模流等外力而不至于塌线、拉出来的线弧形态如何能稳定不损伤、需要的焊线推拉力数值如何能达成、怎样控管好小线径的尺寸、如何在不影响主要特性的情况下替客户降低成本,并且维持线材的抗硫化性等等,都是键合线供货商可以努力的方向。关于不同的键合线特性的不同可参考下方比较表,从表中我们可以很清楚地发现,藉由高金线、合金线等相关产品的使用,不仅能降低20%-40%成本,同时可满足与纯金线不相上下的性能,目前也已通过许多世界级客户的认可,受到业界广泛的使用了。也就是说,选用好的高金线或合金线,是降低成本,且同时做好小芯片封装的关键,如图一所示。

表一、纯金线、高金线、合金线之相关特性比较表

图一、选用好的高金线或合金线,是降低成本,且同时做好小芯片封装的关键

瓷嘴方面的参数优化也很关键,在键合线径必须减小以符合电极焊盘尺寸的前提下,可选用单倒角形态配合针头表面粗糙化的瓷嘴来达到更好的第一焊点强度;此外,使用较大的针头直径(T)、表面角度(FA)搭配较小的外弧半径(OR)可达到更好的第二焊点强度及鱼尾的稳定度。当然,透过实际的状况配合经验来调整出适当的焊线参数如烧球电流、焊线时间、焊线功率…等也是非常重要的。

总的来说,由于优势明显,小芯片的应用是未来LED的趋势之一,无论是大功率照明或是小间距显示屏的发展都与此息息相关,而小芯片封装更是达到此目标的关键技术。要打出好的焊线,除了适当的参数、正确的瓷嘴外,选用质量好的键合线也是非常重要的,这叁者缺一不可,也唯有这叁者都完善了,小芯片封装的技术才会更好。(作者:廖艺泽(1985-),台湾台北人,从事LED封装方面的相关研究)