【导读】高速通信系统已经在世界范围内进入大规模建设阶段,大量的信息交互促进了通信和计算机技术的迅猛发展,高速干线系统作为信息高速公路的主干,研究设计其所采用的高速芯片势在必行。数据的传输方式,由于并行信号彼此之间的耦合与串扰限制了其工作速度和传输距离,而串行方式节约传输媒介,降低了系统互连的复杂性,传输速率更高、距离更远,已在芯片之间、处理器与外设之间、高速硬盘接口、背板连接等领域广泛应用。

为了克服时钟的最大翻转频率受到工艺限制的缺点,简化电路设计的复杂度以及时钟分布的难度,实现更高的速率,同时尽量降低系统功耗,半速率电路结构逐步取代全速率结构“_.本文根据2.5Gbps高速串行收发器的工作实际,为降低后续电路设计难度,采用工作速率较高的电流模式逻辑(Current Mode Logic,CML)设计了双环时钟数据恢复电路中的前端1:2解复用电路,采用SMIC 0.18 um模拟混合信号工艺实现并基于SpectraVerilog进行数模混合仿真,结果显示电路可以正常工作,符合预期要求。

1解复用电路单元

解复用电路把一路高速信号还原为若干路低速信号,常用结构包括串行、并行、树形以及上述3种结构的组合形式。串行解复用电路结构简单,时序关系清楚,可以实现任意1:N的解复用功能,但所有触发器工作在输入时钟频率上,其工作速度会制约电路的速度,因此串行结构对触发器设计和工艺的要求较高,而提高触发器速率会带来芯片功耗增加、电平摆幅减小,噪声容限变小等问题,因此常用于低速系统中;并行结构中触发器工作在输出数据速率上,对触发器速率要求小,因此功耗较低、设计简单,兼顾了速度与功耗,是1:2解复用电路的理想结构,但对于1:N解复用而言,N个并行连接的触发器对前级电路构成很大的电容负载,是速率提升变得困难;树形解复用电路充分利用1:2并行解复用电路的优点,使整个电路较前两种结构有高速低功耗的优点。

对于采用半速率结构的高速串行收发器而言,整个电路性能主要受前端1:2解复用电路的限制,同时考虑到为了增强信号可靠性,待处理的输人数据为差分数据,本文设计的1:2解复用电路采用类并行结构,如图1所示,上下两个电路为采用电流模式逻辑结构的解复用电路单元,输入为差分数据和互补时钟。

图1差分输入互补时钟的1:2解复用电路原理图

电流模式逻辑电路相比传统的CMOS电路可以在更低的信号摆幅情况下工作在更高的频率。基于CML的解复用电路单元原理图如图2所示,其工作原理可以描述为:NMOS管N1L可以看做开关使用,在时钟CKP为低电平期间截止,由N2L、N3L、P1L和P2L构成的输入级处于保持模式,N4L和N5L的漏极被充电到高电平;在时钟CKP为高电平期间导通,输入级处于透明状态,电路接收差分输入数据Din_P和Din_N.电路中由P4L和P6L构成的正反馈电路对前级起到锁存作用,可以加速输出数据的翻转,提高转换速率;左下角的8个晶体管构成平衡负载电路,可以保证N4L和N5L输出线上的负载对称。输入数据在时钟信号控制下送到输出Dout,输出数据与输入数据反相。

图2解复用电路单元原理图

图3解复用单元电路仿真结果

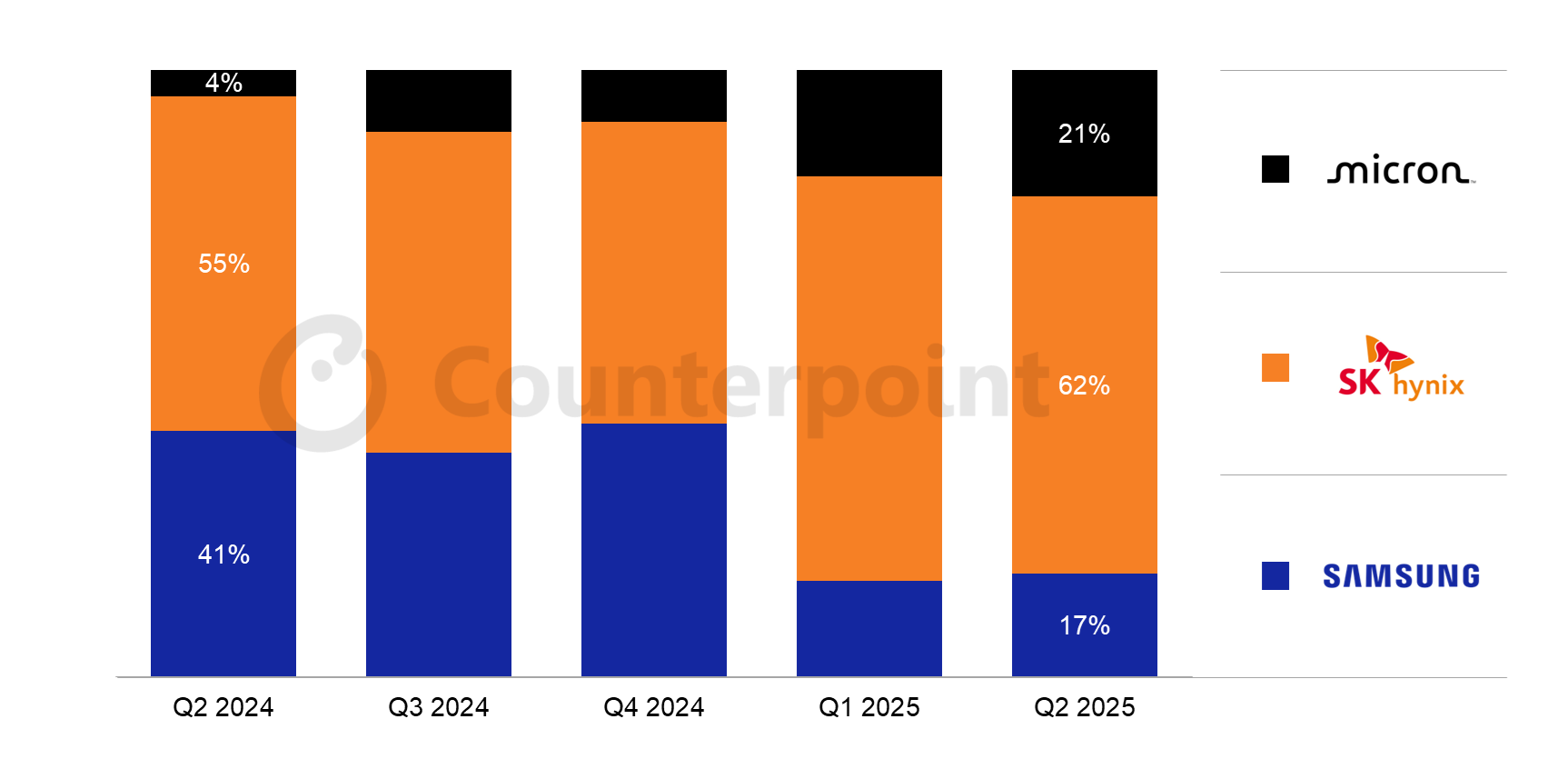

对图1所示的解复用模块进行仿真,输入为由互补的PWL分段线性源指定的位周期为400 ps的差分数据,采用周期T=800 ps,上升时间和下降时间为tr=tf=40 ps的脉冲电压源作为时钟信号,仿真结果如图3所示。从图中可以看出有效数据部分从时钟的第二个高脉冲开始,从仿真结果可知,解复用电路可以正常实现数据1:2的串并转换。

2用于高速收发器的解复用电路

在高速串行收发器的接收端,为了保证数据的鲁棒性和电路工作的可靠性,数据采用差分形式。从第二部分可以看出基于CML的1:2解复用电路可以正常工作,因此可以以此为基础搭建用于高速差分串行数据半速率收发器的前端1:2解复用电路。电路原理图如图4所示。其中clkI与clkIN、clkQ、clkQN为互补时钟,clkI与clkIQ为正交时钟,DinP和DinNer位差分输入的2.5Gbps串行数据,DmP与DmN、DsP与DmN为1:2解复用后的两路1.25Gbps查分数据。

图4差分输入差分输出的1:2解复用电路原理图

图5整体解复用电路的仿真波形图

采用SMIC 0.18um模拟混合信号工艺完成电路设计,现对图4所示解复用单元进行仿真。由于分段线性电压源在表示数据时特别繁琐,而且单个指定数据难以保证仿真的随机性和全面性,故而这里采用数模混合的方法进行仿真。输入数据采用VerilogHDL语言编写的伪随机序列,采用Cadence的SpectreVerilog进行仿真。仿真结果如图5所示,比较输入数据和由主时钟采样输出的数据,可以看出电路的解复用操作是正确的。

本文描述了解复用电路的传统设计方法并分析了各自特点,根据2.5Gbps高速串行收发器的应用实际,采用类并行结构、基于电流模式逻辑设计了收发器的前端解复用电路,并分析了其工作原理,采用SMIC O.18 um混合信号工艺完成了电路设计,并采用SpectreVerilog进行了数模混合仿真,结果表明该电路在2.5Gbps收发器电路中可以稳定可靠地工作。

相关文章

智能网络NS-3 的MANET路由协议性能分析方案

智能网络Atmel和SIGFOX在远程物联网连接领域的设计方案

智能网络基于PIC32的以太网与CAN总线的网桥设计方案