【导读】随着手机及其他便携手持装置的功能不断增加,设计的取舍平衡亦日趋精细。文本信息与网络浏览等流行功能都要求更多的数据输入,而这对于传统的双音多频 键盘会比较困难。使用这种键盘要求多端数据输入,输入效率低而且容易出错。

图 1 – QWERTY 键盘(摩托罗拉 A630)

使文本输入更为方便的一个方法是使用 QWERTY 键盘(见图 1)。这种键盘采用 40 个或更多按键,而 DTMF 手机通常采用 12 个。当然,多出的按键会使手机体积变大,用到的电子组件也更多。

然而,文本信息用户可能乐意以体积换取 QWERTY 键盘,因为文本输入大为简便了,而且两个大拇指都可以用来输入文本信息或数据。最近,有些手机生产商已经推出了面向文本用户的带 QWERTY 键盘的手机。

数据输入键盘可以用多种方法来设计,并无一定之规。为传统 DTMF 键盘添加更多按键对设计人员提出了挑战,本文即讨论应对这挑战的一种可能解决方案。

QWERTY 构建模块

我们的解决方案使用 Xilinx? CoolRunner?-II CPLD" target="_blank">CPLD;低功耗、小包装及低成本的特点使其成为此应用的理想选择。

将 DTMF 转化为 QWERTY 键盘需要更多按键,从而需要更多通用 I/O (GPIO" target="_blank">GPIO)。例如,DTMF 键盘可能只有四行三列,而 QWERTY 键盘可能有多至八行八列。不过,键盘的大小可根据终端系统的需求而定。

通常,将处理器或 DSP 用作连接键盘行和列的界面(见图 2)。处理器对行进行扫描,对列进行监控,以检测逻辑变化。当变化发生,即表示用户按下了一个按键。知道被扫描的是哪一行,以及哪一列的状态发生了变化,处理器即可推断出按下的是哪个按键。

扩展 I/O

设计需要更多 I/O 的键盘时(QWERTY 键盘即为一例),可能会发现现有处理器没有足够的 GPIO。一种可能的解决方法是,把一个 CPLD 用作 I/O 扩展器,从而减少对处理器 I/O 数量的要求。

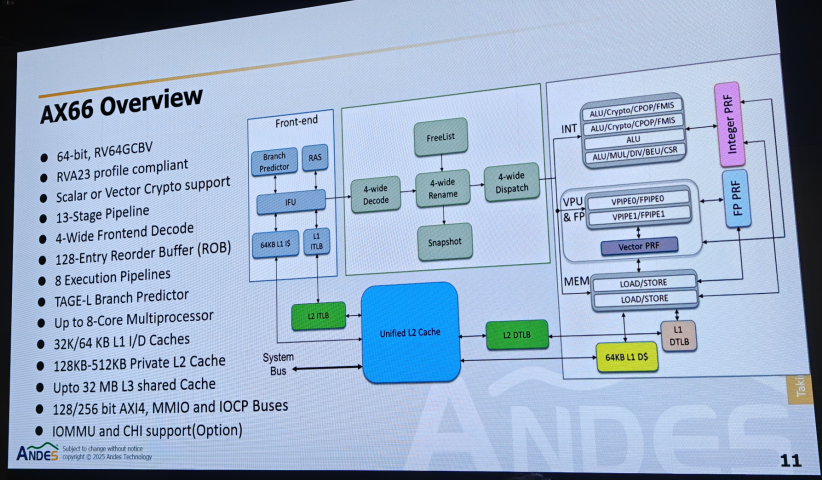

图 3 在处理器与键盘之间使用了一个 CPLD,其一侧连接键盘的行/列,另一侧连接处理器的可用 GPIO。此例中,使用一个 CPLD 后,一个 8 x 8 的键盘所需要的处理器 GPIO 端口的数目与 4 x 4 的键盘相同(实际上还少一个)。如果不使用 CPLD,处理器会需要 16 个 GPIO 端口,而不是 7 个。

扫描与编码

除了减少处理器对 GPIO 的数量要求外,CPLD 还可以承担处理器的某些功能,如:对行进行扫描并对列进行监控以检测状态变化。当用户按键时,CPLD 会停止扫描,并立即生成一个编码字,然后发送给处理器,告诉处理器哪个键按下了。因为使用了编码字来告知处理器按下了哪个按键,对处理器的 I/O 需求得以减轻。

– 使用 CoolRunner-II CPLD 扩展 GPIO

在图 3 所示例子中,用 6 个位来代表编码字。6 个位提供 26(即 64)个不同的值,每个值代表一个按键。然而,还必须有一个值代表无按键被按时的状态。因此,在此例中,在不添加又一个 GPIO 的情况下,实际上只有 63 个按键可被代表。

处理器无需扫描键盘,因为这一操作现由 CPLD 执行;不过,处理器仍需监控其 GPIO 上的变化 – 它只是不再需要推断哪个按键被按,因为该信息编码到一个六位字中了。

还需要用到的是开关抖动,这可以安排在 CPLD 中或处理器中,取决于哪个装置有可用资源。在处理器中进行这一操作,可将 CPLD 的大小和成本降到最小。

简要总结此设计示例:CPLD 对键盘进行扫描,检测被按下的按键,然后提供一个编码字供处理器读取并解析。这一功能不仅使处理器不必再承担扫描任务,还扩展了 GPIO 的功能。

此设计非常适合于 CoolRunner-II 32 宏单元装置(利用率大约为 75%),留下 25% 空间作他用。此外,此设计还采用了其他一些方法来减少功耗并利用 CoolRunner-II 的节能功能。

CPLD 设计详述

要扫描键盘的行,桶式移位寄存器除一位预置为零外,其他所有位均预置为 1。移位寄存器的每一位驱动 CPLD 上的一个输出引脚,后者与键盘的行相连。当移位寄存器开始计时时,零位通过桶式移位器移位,将行逐行置低,以对其进行扫描。键盘的列输入到 CPLD,每个输入都通过一个内部上拉电阻上拉。

当没有按键被按时,CPLD 的所有列输入都被动上拉至逻辑高位。对所有的列输入一起进行“与”操作,这时输出端的逻辑 1 表示没有按键被按。

“与”操作的输出用于启动移位寄存器。当按键被按下时,列与行取得连接,按下的键所在的列被与该按键相关的行置低。“与”操作的输出将变为零,从而在按键被按下时中止移位寄存器。

图 4 – 模块图

此时,移位寄存器将按下的键所在的行置低,而该键所在的列亦处于低位。为了使这些信息相关联,使用了两个编码器:一个用于行位(移位寄存器的输出),另一个用于列输入。两个编码器的输出组合起来,就构成发送给处理器的编码字。图 4 为这一操作的模块图。

使用 Xilinx CoolRunner-II CPLD,获得的是灵动的设计与低功耗。除了 I/O 扩展之外,CPLD 还可以加入其他“粘合”功能,如:电压转换、I/O 标准转换与输入滞后。

由于 CPLD 为可编程,您可以将同一装置用于不同的键盘和产品,而收高产量低成本之效。可再编程的特点辅之以简便易用的设计工具,使您可以对设计进行晚期更改,降低风险。

相关文章

应用于智能手机ERM及LRA执行器的起动与停止性能的设计方案

智能手机TPA2028D1对突发音信号(短暂提示音)的响应设计方案

应用于智能手机的键盘控制器实现方法比较方案