发布时间:2014-05-9 阅读量:800 来源: 发布人:

大部分采用Cortex-M3/M4 MCU的目标应用是便携式的,并且供电电源来自电池或能源收集系统,因此我们所探讨的大部分概念涉及如何减少系统整体能耗的技术。然而,在许多情况下,这些节能技术也是处理器应用设计的有力工具,可提供:

●更符合成本效益的解决方案

●更大的升级和采用新特性的设计冗余

●有助于产品在激烈竞争市场上脱颖而出的性能和特性

小知识:Cortex-M3对比Cortex-M4

Cortex-M3架构背后的指导思路是设计一种既要满足应用的成本效益又要提供高性能计算和控制1的处理器。类似的应用包括汽车车身系统、工业控制系统和无线网络/传感器产品等。M3系列为32位的ARM处理器架构引进了多项重要特性,包括:

●不可屏蔽式中断

●高度确定性、嵌套、向量式中断

●原子位操作

●可选的存储保护(MPU)

除了绝佳的计算性能,Cortex-M3处理器先进的中断结构还能确保系统迅速响应真实世界的事件,同时仍然提供极低的动态与静态功耗。

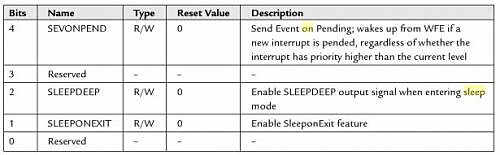

图1 ARM Cortex M3和M4对比

进入正题

SWO接口节省I/O引脚并加速调试

除了传统的串行调试(Serial Wire Debug)功能之外,基于ARM Cortex-M的MCU还可以通过它的单引脚串行监视器输出(Serial Wire Viewer Output,SWO)3提供指令跟踪接口,如图2所示。这个接口可以直接把“printf格式的”调试信息传递给应用代码。SWO允许调试信息直接在任何标准的IDE中浏览。此外,这些信息也可以用独立的SWO监视器(例如,Segger的J-Link SWO Viewer软件4,或是Silicon Labs的energyAware Commander 4)进行浏览。由于SWO输出内建于内核硬件本身,因此它是Cortex-M内核与生俱来的优点。SWO不占用MCU的任何UART接口,这些接口它们可能早已被分配给了应用。

图2 专用ARM Cortex SWO接口节省I/O引脚并加速调试

基于SWO的调试还有一个重要的优势在于,它让微控制器在进入最低的休眠模式时,保持调试连接有效,而在大多数情况下,传统的调试连接这时是不能正常工作的。SWO的指令追踪还可以用于跟踪程序计数器,以帮忙IDE统计出程序各项功能所占用的时间。这些统计数字能够与电流测量结合起来,帮助开发人员对设计功耗进行微调。

目前一些供应商正在开始重新认识这项优点,而且有些厂商已经为了这个目的而把功耗模式和电流测量硬件纳入到本身的开发平台。例如,Silicon Labs的EFM32 Gecko MCU入门级和开发级工具包都包含功耗测量输出,并可搭配energyAware Profiler工具6中的程序代码追踪功能。图3显示了如何让设计人员精确定位到哪个程序功能块最耗费能源,并且能够快速调试其它与能源有关的问题。

图3 软硬件工具精确定位耗能最大的功能,无需示波器和万用表,快速排除问题

智能休眠节省每一微瓦

ARM Cortex-M处理器的Sleep-on-Exit(中断完成时直接进入休眠)是另一项“一箭双雕”的功能,可同时节省CPU周期和能耗。这点在由中断所驱动的应用中格外有用,因为处理器的大部分时间不是在执行中断处理,就是在中断事件之间休眠。在进入中断服务例程(ISR)时,MCU必须花费好几个指令周期把当前线程状态入栈,然后在退出中断处理返回时恢复原有线程状态,即“出栈”。当应用需要处理器在退出ISR后直接进入休眠状态时,传统MCU仍然必须恢复原先存储的状态信息,然后线程代码才能让MCU进入休眠状态。同样地,当下次的中断唤醒MCU时,它的状态必须再次入栈。

而当使能ARM Cortex-M微控制器上的Sleep-on-Exit功能后,MCU就会在中断处理完成后直接进入休眠状态,而不用先返回到原有线程上(见图4)。这会使处理器仍然保持在中断状态,因为消除了唤醒再入栈过程,因而节省下许多宝贵的机器周期。消除入栈出栈过程既节省了时间也节省了能耗,否则电能就会被不必要的指令周期白白消耗,也包括哪些传统MCU在休眠和唤醒之间管理堆栈的代码。而且,当处理器被中止调试请求(Halt Debug Request)唤醒时,出栈过程将会自动进行。

图4:ARM Cortex-M的Sleep-on-Exit功能通过避免不必要的代码执行和减少出栈入栈操作降低功耗

ARM Cortex-M4运行更快、休眠功耗更低

像许多MCU一样,Cortex-M3/4处理器通常能够采用高时钟速率的方法在中断驱动的应用中节省能耗。如果处理器大部分时间处于休眠状态,这种看似违背直觉但普遍采用的节能策略就会很好,因为运行时间减少所节省的能耗远远大于稍高的操作电流。简单来说,多花10%的电可以省掉20%的时间,总体来说是节能了。

这种技术可以应用在任何Cortex-M系列的处理器上,而涉及密集运算任务的应用也能从Cortex-M4处理器的额外能力中受益。它的单周期DSP指令和可选的浮点加速器能大大减少诸如数字信号处理、过滤、分析或波形合成等功能所需要的执行周期数。

上面提及的节能特性也能带来其它优势。例如,在超音波/声学水表之类的应用中,它们必须在小电池供电下运行多年,需要MCU尽可能长的保持在休眠状态。除了有助于减少MCU唤醒时间之外,Cortex-4 DSP和浮点算术指令也能使用成熟的滤波功能从廉价声学传感器输出中获得所需的信息,从而避免采用昂贵的超声波流量传感器。在这个应用实例中,Wonder Gecko MCU的外设还能够作为模拟状态机提供额外的能量节省,它仅仅在需要时才唤醒Cortex-M4处理器。

虽然并不完备,但这些林林总总的秘诀与妙方应该能让各位产生好的思路,可以在下一次设计中充分利用Cortex-M系列中一些较不为人知的特性所带来的好处。为了发挥ARM Cortex-M系列的这些和其它重要功能,可参考本文末段的参考资料,它们提供了所需的更多细节。

在电子工程领域,频率响应分析(Bode分析)一直是电路设计和调试的重要工具。然而,专业网络分析仪的高昂价格让许多人望而却步,一个令人惊喜的解决方案——共模扼流圈与示波器的黄金组合,可以极低成本实现专业级Bode分析。通过巧妙利用共模扼流圈的独特特性,配合普通示波器的基本功能,即使是预算有限的爱好者也能获得准确的频率响应曲线。

在现代电子设备中,USB接口已成为数据传输和电力供应的标准配置。一个优秀的USB接口PCB设计不仅能确保信号完整性,还能最大限度地发挥接口的理论传输速度

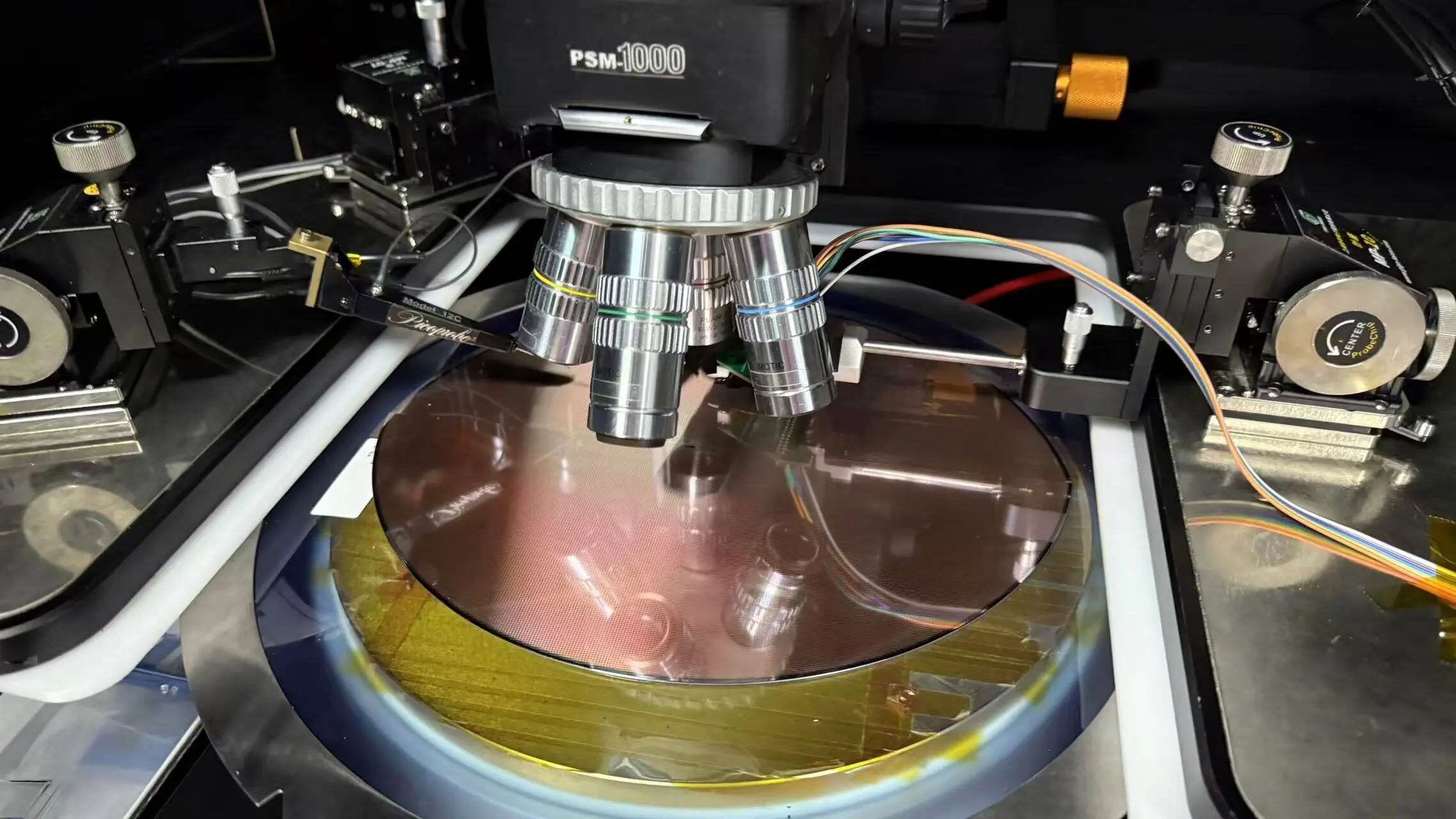

8月21日,中国半导体行业迎来里程碑式进展——领开半导体成功研发并量产28nm以下嵌入式闪存(e-Flash)技术,一举打破国外厂商在该领域的长期垄断。这一突破不仅填补了国内高端存储芯片的技术空白,更为国产MCU、汽车电子及AIoT设备的自主可控提供了关键支撑。

近日,有外媒报道称,美国特朗普政府正考虑以“国家安全”为由,强行入股包括英特尔在内的三大芯片巨头,以加强对半导体产业的控制。这一消息迅速引发行业震动,外界担忧此举可能重塑全球芯片产业格局,并对供应链产生深远影响。

在全球科技竞争格局深刻重构的背景下,中国电子产业正迎来国产替代与自主创新的历史性机遇。第106届中国电子展紧扣《"十四五"规划》制造强国战略,聚焦基础电子元器件、集成电路等"卡脖子"领域,集中展示从材料、设备到应用的国产化突破成果。