发布时间:2014-04-18 阅读量:856 来源: 我爱方案网 作者:

热门资讯阅读:

谷歌建模手机Project Tango 用3D成像改变人们的交互方式

新思科技Verification Compiler验证编译器使产能提升3倍

Synopsys推出业界最快的仿真系统ZeBu Server-3

Mouser宣布赞助EasySim和EasyPCB在线免费设计工具

TI建立物联网云生态系统 帮助制造商实现更多互联

亮点:

1、设计规划速度提升了10倍,实现速度提升了5倍,容量提升了2倍 – 它们共同使吞吐量加速了10倍

2、构建于全新的可扩展基础架构、时序和解析优化引擎之上

3、已经在成熟和新兴的技术节点上成功生产流片

为加速芯片和电子系统创新而提供软件、知识产权(IP)及服务的全球性领先供应商新思科技公司今日宣布:正式推出将导致游戏规则发生改变的IC Compiler II,它是当前领先业界的布局和布线解决方案IC Compiler的继任产品,可用于基于成熟和新兴工艺节点的先进设计。得益于在一种全新的多线程架构上完全重构,IC Compiler II引入了超高容量设计规划、独特的时钟构建技术以及先进的global-analytical收敛技术。IC Compiler II通过使物理设计的吞吐量实现了10倍的加速,将产能引入到了一个全新的时代,同时它已经帮助领先客户成功流片。其中的几位客户将在Synopsys用户大会(SNUG)硅谷站分享他们使用IC Compiler II的经验,该大会将在Santa Clara会议中心举办。了解早期伙伴使用IC Compiler II的经验。

“从RTL综合到静态时序再到物理综合,Synopsys走出的创新之道已经改变了电子设计。借助IC Compiler II,我们正在接近另一个转折关头。”Synopsys执行副总裁兼设计业务部总经理Antun Domic表示道:“由于面向更高速度全面重构,同时结合了全新开发的算法途径,这项全新的解决方案在吞吐量方面带来无可比拟的改善,为物理设计开启了通往全新天地的大门。”

Synopsys的IC Compiler长期以来一直被认为是先进的高性能设计的明智之选,适用于新兴的、以及成熟的硅工艺技术节点。在几年前,当不断投资以确保IC Compiler保持其领先性时,Synopsys就开始构建一种全新的布局布线系统,其目的是使设计师的产能实现一个数量级的飞跃。Synopsys特有的各种资源组合使这项超大型任务成为可能,包括:雄厚的资源储备去维持各项并行开发的投入,先进的专业技术以追求核心算法中的根本性突破,以及广泛的客户合作提供了实际设计中的使用情况反馈并不断完善新技术,这一举措成就了Synopsys最新的布局布线解决方案IC Compiler II。Synopsys将继续加强和支持IC Compiler,为希望继续使用它的客户提供灵活的选择,在客户选定的时间点上提供升级到IC Compiler II的机会。

IC Compiler II是一种全功能的布局布线系统,其核心是一种全新的多线程基础架构,能够处理例化单元数量大于5亿的设计。为了充分体现其“可重新思考、可重新构建和可重新使用”的开发策略,IC Compiler II基于行业标准的输入和输出格式,以及熟悉的界面和工艺技术文件,同时引进了创新设计存储功能。IC Compiler II从开发之初就关注全芯片级设计,部署新颖的设计规划功能,并使其性能提升了10倍,内存占用则减少了5倍。这使设计人员能够快速地评估多种可选芯片布局方案,以确定设计实现的最佳起点。与这些芯片级功能互补的是单元模块级的功能,它得到了一个新的global-analytical优化引擎、一个全新的时钟发生器以及独特的布线后优化算法功能所支持, 它们结合在一起共同提高了面积、时序和功耗的结果质量(QoR)。IC Compiler II还包含了IC Compiler中所采用的先进技术,例如共轭梯度布局器和ZRoute布线器。与现有的解决方案相比,IC Compiler II使运行时间平均提高5倍,所需内存平均降低2倍。通过将运行时间加速、高超的芯片布局、可实现的QoR以及高效的轻量级环境相结合,能够减少设计迭代次数,进一步提高设计产能。

IC Compiler II开发过程也得益于与一些全球领先的设计团队的密切合作。将于2014年年中开始供货。

关于新思科技

Synopsys加速了全球电子市场中的创新。作为电子设计自动化(EDA)和半导体IP领域内的一位领导者,其软件、IP和设计服务帮助工程师应对设计、验证、系统和制造中的各种挑战。自1986年以来,全世界的工程师使用Synopsys的技术已经设计和创造了数十亿个芯片和系统。

在电子工程领域,频率响应分析(Bode分析)一直是电路设计和调试的重要工具。然而,专业网络分析仪的高昂价格让许多人望而却步,一个令人惊喜的解决方案——共模扼流圈与示波器的黄金组合,可以极低成本实现专业级Bode分析。通过巧妙利用共模扼流圈的独特特性,配合普通示波器的基本功能,即使是预算有限的爱好者也能获得准确的频率响应曲线。

在现代电子设备中,USB接口已成为数据传输和电力供应的标准配置。一个优秀的USB接口PCB设计不仅能确保信号完整性,还能最大限度地发挥接口的理论传输速度

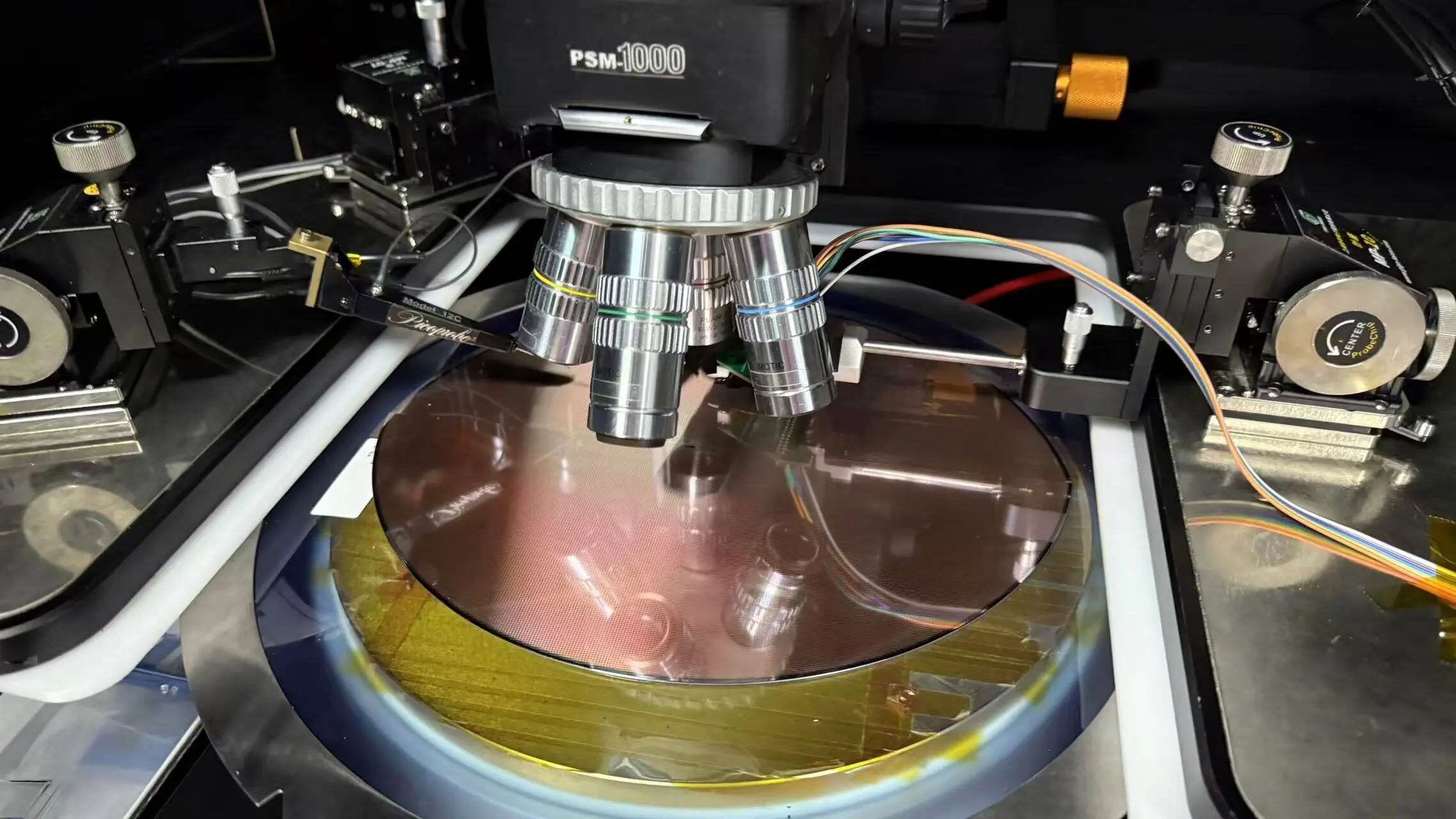

8月21日,中国半导体行业迎来里程碑式进展——领开半导体成功研发并量产28nm以下嵌入式闪存(e-Flash)技术,一举打破国外厂商在该领域的长期垄断。这一突破不仅填补了国内高端存储芯片的技术空白,更为国产MCU、汽车电子及AIoT设备的自主可控提供了关键支撑。

近日,有外媒报道称,美国特朗普政府正考虑以“国家安全”为由,强行入股包括英特尔在内的三大芯片巨头,以加强对半导体产业的控制。这一消息迅速引发行业震动,外界担忧此举可能重塑全球芯片产业格局,并对供应链产生深远影响。

在全球科技竞争格局深刻重构的背景下,中国电子产业正迎来国产替代与自主创新的历史性机遇。第106届中国电子展紧扣《"十四五"规划》制造强国战略,聚焦基础电子元器件、集成电路等"卡脖子"领域,集中展示从材料、设备到应用的国产化突破成果。