发布时间:2012-11-14 阅读量:682 来源: 我爱方案网 作者:

国际半导体产业协会(SEMI)最新报告指出,生成式AI需求的爆发正推动全球芯片制造产能加速扩张。预计至2028年,全球12英寸晶圆月产能将达1,110万片,2024-2028年复合增长率达7%。其中,7nm及以下先进制程产能增速尤为显著,将从2024年的每月85万片增至2028年的140万片,年复合增长率14%(行业平均的2倍),占全球总产能比例提升至12.6%。

据供应链消息确认,高通新一代旗舰芯片骁龙8 Elite Gen 2(代号SM8850)将首次采用双轨代工策略:台积电负责基于N3P(3nm增强版)工艺的通用版本,供应主流安卓厂商;而三星则承接其2nm工艺(SF2)专属版本,专供2026年三星Galaxy S26系列旗舰机。此举标志着高通打破台积电独家代工依赖,三星先进制程首次打入头部客户供应链。

在AI算力需求爆发性增长的浪潮下,存储巨头美光科技交出超预期答卷。其2025财年第三季度营收达93亿美元,创历史新高,其中高带宽内存(HBM)业务以环比50%的增速成为核心引擎。凭借全球首款12层堆叠HBM3E的量产突破,美光不仅获得AMD、英伟达等头部客户订单,更计划在2025年末将HBM市占率提升至24%,直逼行业双寡头。随着下一代HBM4基于1β制程的性能优势验证完成,一场由技术迭代驱动的存储市场格局重构已然开启。

随着汽车智能化升级,高保真低延迟高集成度的音频系统成为智能座舱的核心需求。意法半导体(ST)推出的HFDA80D和HFDA90D车规级D类音频功放,以2MHz高频开关技术数字输入接口及先进诊断功能,为车载音频设计带来突破性解决方案。

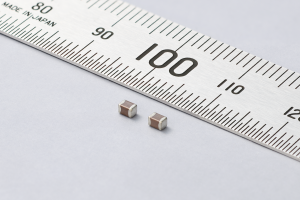

随着汽车智能化电动化进程加速,自动驾驶(AD)和高级驾驶辅助系统(ADAS)等关键技术模块已成为现代车辆标配。这些系统依赖于大量高性能电子控制单元(ECU)和传感器,导致车内电子元件数量激增。作为电路稳压滤波的核心元件,多层片式陶瓷电容器(MLCC)的需求随之水涨船高,尤其是在集成电路(IC)周边,对大容量电容的需求尤为迫切。然而,有限的电路板空间与日益增长的元件数量及性能要求形成了尖锐矛盾,元件的高性能化与小型化成为行业亟待攻克的关键难题。