中心议题:

* FPGA行业进入硅片融合时代

* 3D封装和软件是硅融合时代的技术挑战

经过20年的发展,寡头垄断的FPAG行业的竞争格局正在发生悄然的变化,FPGA厂商竞争的焦点正在从工艺节点的比拼,转向应用设计导向的硅片融合能力 的提升——这就是日前Altera公司资深副总裁,首席技术官Misha Burich博士接受我爱方案网采访时,传递出的重要信息。

工艺进步:FPGA发展达到关键点

FPGA与ASIC相互之间的市场渗透,一直是业界关注的热点话题。Misha Burich博士认为,在过去的10年中,随着工艺的进步,可编程逻辑器件(PLD)在工艺和总体拥有成本上已经超越了传统的ASIC。在他为我们展示的 工艺节点演进图中,2003年之后传统ASIC的工艺一直维持在130nm,而在2005年,PLD的工艺水平首次超越ASIC达到了90nm,之后在 2008年达到了关键的40nm——在这个工艺节点上,采用40nm工艺的FPGA和采用130nm工艺的ASIC在芯片面积上已经基本相同,在结构化 ASIC上甚至更具优势——在之后的几年中,随着PLD工艺水平的进步,与ASIC相比,FPGA已经具有了明显的竞争优势。可以说,工艺进步为FPGA 进入硅片融合时代,奠定了坚实的基础。

图一,PLD与ASIC工艺演进路线图

灵活性和效率需求:FPGA架构走向融合

而真正推动硅片融合时代到来的,是设计需求。Misha Burich博士分析,通常设计者在选择开发平台时,有三种选择:通用处理器和DSP,这个平台灵活性强,软件可编程,但是缺点是运算的功效(单位任务的 功耗)比较低;而ASIC和ASSP,由于是针对特定应用进行的优化设计,运算功效高,但是不可编程,灵活度差;而介于二者之间,以FPGA为代表的 PLD,由于支持硬件可编程,灵活度高,且具有比较好的效率。当今的电子产品设计越来越强调灵活性和效率兼顾,而达到这一目的最佳的选择就是建立一个包含 处理器和硬件逻辑的“混合系统架构”。

尽管通用处理器厂商通过优化效率,ASIC/ASSP厂商通过引入嵌入式处理器增强灵活性,都在尝试构建这样一个理想化的平台架构,但是Misha Burich认为,在建立一种包含微处理器、DSP、专用IP和可编程逻辑单元在内的混合系统架构上,FPGA与其他设计平台相比具有天然的优势——这种 优势不仅来自于FPGA厂商原有的平台架构基础,还来自与已经拥有的完善的生态系统。

Misha Burich举例,Altera公司不仅有自己开发的Nios软核处理器,还与ARM、MIPS、Intel等嵌入式处理器厂商建立了良好的合作;在硬件 逻辑电路方面,Altera有HardCopy的基础;同时公司拥有DSP高级模块库,可提供浮点DSP和精度可调的DSP;此外,公司还通过并购,不断 扩展面向应用市场的IP库。这些资源都有助于Altara建立一个强大的硅片融合系统。

Misha Burich博士还分析,这一趋势一直影响着FPGA体系架构的演进,上个世纪90年代,FPGA主要替代了胶合逻辑;到了2000年,FPGA平台中加 入DSP和其他硬件逻辑电路,在通信、军事、测试测量、医疗等市场中,替代了ASIC、ASSP和DSP的应用;而在下一个10年中,由于整合了更加丰富 的资源,FPGA的应用会扩展到更广的应用领域,向微处理器的市场的渗透将会加速。在Altera最新的Stratix FPGA平台中,可编程逻辑单元的面积已经少于50%,可见硅片融合趋势之强烈。

图二,FPGA系统架构的演进显示硅融合趋势明显

应用拉动:FPGA市场迅速扩展

硅片融合使得设计平台的性能显著提升,随之而来的就是应用范围的拓展。Misha Burich博士为我们展示了硅片融合时代FPGA应用蓝图。首先,在高性能计算领域,有报道称IBM计划将增加对FPGA的关注,因为FPGA与多核处 理器相比可以实现更高的效率。其次,在存储领域,FPGA在固态硬盘中也有成功应用——Vision Memory公司在完成RAID、页面映射和垃圾收集功能方面,由于采用了FPGA缩短了延时,大大提高了持续随机写IOPS,和其他固态硬盘使用处理器 和软件的方案相比优势明显。

在工业领域FPGA还可以用于高能效的电机驱动,在Misha Burich展示的方案中,第一阶段FPGA作为原有DSP/MCU控制系统的补充,可以为电机控制系统提供I/O扩展和工业以太网等通信功能的支持。而 未来采用SoC FPGA可以实现3个电机及安全支持,每个电机的BOM成本会降低50%,同时在功耗上,也会有明显的改善——从3.2W,480MIPS优化至 2W,1500MIPS。

.jpg)

图三,采用SOC FPGA实现的工业电机控制系统

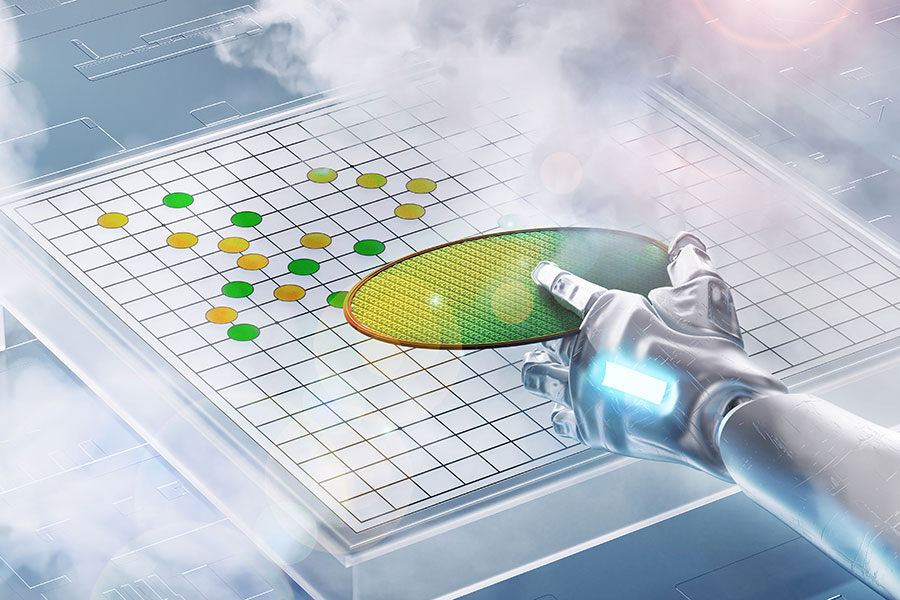

FPGA的硅片融合之路,也面临着诸多技术上的挑战,Misha Burich博士分析,最值得关注的就是来自与3D封装和软件开发环境。

为了能够将多种资源快速“融合”在一个器件中,立体化的封装形式是必然之选。Misha Burich博士介绍,到达最终的3D封装还需假以时日,目前2.5D异构封装是最为现实的选择,Altera正在采用TSMC的CoWoS(基底晶圆芯 片)技术,将芯片的制造和封装合并在一起,目前公司的第一款异构测试芯片已经完成。同时Altera还加入了IMEC的3D封装研究计划,推动3D封装技 术的发展。

面对更复杂的混合系统架构,必须建立起与之对应的开发环境。Misha Burich博士表示,Altera早就意识到“让用户更好地应用硬件完成设计,比硬件本身更重要”,因此公司在软件开发环境上投入了巨大的资源——目前 公司研发团队的50%在从事软件开发工作。目前Altera已经建立起了包括嵌入式软件工具、可编程硬件设计、系统互联、DSP编程和基于C语言的编程工 具,完整的开发工具体系。特别是Altera加入了Open CL,可以支持编程人员更便捷地使用Altera的硬件技术,建立开发的体系,提升设计效率。

.jpg)

图四,Altera推出的Open CL开发系统

.png)

.jpg)

.jpg)

.jpg)

.jpg)