发布时间:2011-04-26 阅读量:2301 来源: 发布人:

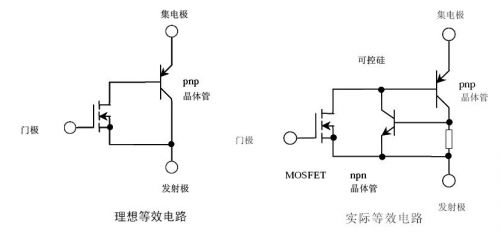

理想等效电路与实际等效电路如图所示:

IGBT 的静态特性一般用不到,暂时不用考虑,重点考虑动态特性(开关特性)。

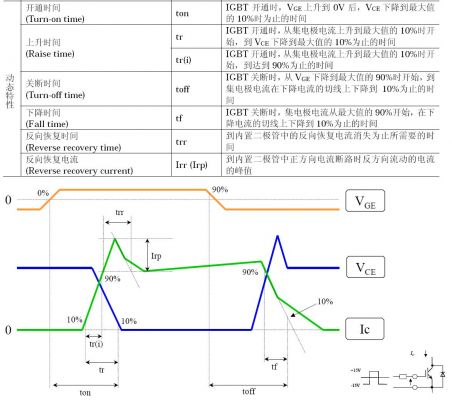

动态特性的简易过程可从下面的表格和图形中获取:

IGBT的开通过程

IGBT 在开通过程中,分为几段时间

1.与MOSFET类似的开通过程,也是分为三段的充电时间

2.只是在漏源DS电压下降过程后期,PNP晶体管由放大区至饱和过程中增加了一段延迟时间。

在上面的表格中,定义了了:开通时间Ton,上升时间Tr和Tr.i

除了这两个时间以外,还有一个时间为开通延迟时间td.on:td.on=Ton-Tr.i

IGBT在关断过程

IGBT在关断过程中,漏极电流的波形变为两段。

第一段是按照MOS管关断的特性的

第二段是在MOSFET关断后,PNP晶体管上存储的电荷难以迅速释放,造成漏极电流较长的尾部时间。

在上面的表格中,定义了了:关断时间Toff,下降时间Tf和Tf.i

除了表格中以外,还定义trv为DS端电压的上升时间和关断延迟时间td(off)。

漏极电流的下降时间Tf由图中的t(f1)和t(f2)两段组成,而总的关断时间可以称为toff=td(off)+trv十t(f),td(off)+trv之和又称为存储时间。

从下面图中可看出详细的栅极电流和栅极电压,CE电流和CE电压的关系:

从另外一张图中细看MOS管与IGBT管栅极特性可能更有一个清楚的概念:

开启过程

关断过程

尝试去计算IGBT的开启过程,主要是时间和门电阻的散热情况。

C.GE 栅极-发射极电容

C.CE 集电极-发射极电容

C.GC 门级-集电极电容(米勒电容)

Cies = CGE + CGC 输入电容

Cres = CGC 反向电容

Coes = CGC + CCE 输出电容

根据充电的详细过程,可以下图所示的过程进行分析

对应的电流可简单用下图所示:

第1阶段:栅级电流对电容CGE进行充电,栅射电压VGE上升到开启阈值电压VGE(th)。这个过程电流很大,甚至可以达到几安培的瞬态电流。在这个阶 段,集电极是没有电流的,极电压也没有变化,这段时间也就是死区时间,由于只对GE电容充电,相对来说这是比较容易计算的,由于我们采用电压源供电,这段 曲线确实是一阶指数曲线。

第2阶段:栅极电流对Cge和Cgc电容充电,IGBT的开始开启的过程了,集电极电流开始增加,达到最大负载电流电流IC,由于存在二极管的反向恢复电流,因此这个过程与MOS管的过程略有不同,同时栅极电压也达到了米勒平台电压。

第3阶段:栅极电流对Cge和Cgc电容充电,这个时候VGE是完全不变的,值得我们注意的是Vce的变化非常快。

第4阶段:栅极电流对Cge和Cgc电容充电,随着Vce缓慢变化成稳态电压,米勒电容也随着电压的减小而增大。Vge仍旧维持在米勒平台上。

第5阶段:这个时候栅极电流继续对Cge充电,Vge电压开始上升,整个IGBT完全打开。

我的一个同事在做这个将整个过程等效为一阶过程。

如果以这个电路作为驱动电路的话:

驱动的等效电路可以表示为:

利用RC的充放电曲线可得出时间和电阻的功率。

这么算的话,就等于用指数曲线,代替了整个上升过程,结果与等效的过程还是有些差距的。

不过由于C.GE,C.CE,C.GC是变化的,而且电容两端的电压时刻在变化,我们无法完全整理出一条思路来。

很多供应商都是推荐使用Qg来做运算,计算方法也可以整理出来,唯一的变化在于Qg是在一定条件下测定的,我们并不知道这种做法的容差是多少。

我觉得这种做法的最大的问题是把整个Tsw全部作为充放电的时间,对此还是略有些疑惑的。

说说我个人的看法,对这个问题,定量的去计算得到整个时间非常困难,其实就是仿真也是通过数字建模之后进行实时计算的结果,这个模型与实际的条件进行对比也可能有很大的差距。

因此如果有人要核算整个栅极控制时序和时间,利用电容充电的办法大致给出一个很粗略的结果是可以的,如果要精确的,算不出来。

对于门级电阻来说,每次开关都属于瞬态功耗,可以使用以前介绍过的电阻的瞬态功率进行验算吧。

电阻抗脉冲能力

我们选电阻的大小是为了提供足够的电流,也是为了足够自身散热情况。

前级的三极管,这个三极管的速度要非常快,否则如果进入饱和的时间不够短,在充电的时候将可能有钳制作用,因此我对于这个电路的看法是一定要做测试。空载的和带负载的,可能情况有很大的差异。

栅极驱动的改进历程和办法(针对米勒平台关断特性)

前面都讲了一些计算的东西,这次总结一些设计法则。

栅极电阻:其目的是改善控制脉冲上升沿和下降沿的斜率,并且防止寄生电感与电容振荡,限制IGBT集电极电压的尖脉冲值。

栅极电阻值小——充放电较快,能减小开关时间和开关损耗,增强工作的耐固性,避免带来因dv/dt的误导通。缺点是电路中存在杂散电感在IGBT上产生大的电压尖峰,使得栅极承受噪声能力小,易产生寄生振荡。

栅极电阻值大——充放电较慢,开关时间和开关损耗增大。

一般的:开通电压15V±10%的正栅极电压,可产生完全饱和,而且开关损耗最小,当《12V时通态损耗加大,》20V时难以实现过流及短路保护。关断偏压-5到-15V目的是出现噪声仍可有效关断,并可减小关断损耗最佳值约为-8~10V。

IGBT内部的续流二极管的开关特性也受栅极电阻的影响,并也会限制我们选取栅极阻抗的最小值。IGBT的导通开关速度实质上只能与所用续流二极管反向恢 复特性相兼容的水平。栅极电阻的减小不仅增大了IGBT的过电压应力,而且由于IGBT模块中di/dt的增大,也增大了续流二极管的过压极限。

栅极电阻与关断变化图

栅极驱动的印刷电路板布线需要非常注意,核心问题是降低寄生电感,对防止潜在的振荡,栅极电压上升速率,噪音损耗的降低,降低栅极电压的需求或减小栅极保护电路的效率有较大的影响。

措施

因此将驱动至栅极的引线加粗,将之间的寄生电感减至最低。控制板与栅极驱动电路需要防止功率电路和控制电路之间的电感耦合。

当控制板和IGBT控制端子不能直接连接时,考虑用双股绞线(2转/CM小于3CM长)或带状线,同轴线进行连接。

栅极保护

为了保险起见,可采用TVS等栅极箝位保护电路,考虑放置于靠近IGBT模块的栅极和发射极控制端子附近。IGBT基础与运用-2 中英飞凌的电路比较典型。

耦合干扰与噪声

IGBT的开关会使用相互电位改变,PCB板的连线之间彼此不宜太近,过高的dv/dt会由寄生电容产生耦合噪声。要减少器件之间的寄生电容,避免产生耦合噪声。

由于IGBT等功率器件都存在一定的结电容,所以会造成器件导通关断的延迟现象。虽然我们尽量考虑去降低该影响(提高控制极驱动电压电流,设置结电容释放 回路等)。但是为了防止关断延迟效应造成上下桥臂直通,因为一个桥臂未完全关断,而另一桥臂又处于导通状态,直通炸模块后后果非常严重(最好的结果是过 热)。

在控制中,人为加入上下桥臂同时关断时间,以保证驱动的安全性。死区时间大,模块工作更加可靠,但会带来输出波形的失真及降低输出效率。死区时间小,输出波形要好一些,只是会降低可靠性,一般为us级,典型数值在3us以上。

在汽车电子应用中,特别要注意环境温度对toff的影响很大,使得toff延长,并且栅极电阻的加入也是的关断时间受一定的影响,因此需要进行调整。

IGBT栅极引起的问题列表(红色部分圈注的):

全球领先的传感器与功率IC解决方案供应商Allegro MicroSystems(纳斯达克:ALGM)于7月31日披露截至2025年6月27日的2025财年第一季度财务报告。数据显示,公司当季实现营业收入2.03亿美元,较去年同期大幅提升22%,创下历史同期新高。业绩增长主要源于电动汽车和工业两大核心板块的强劲需求,其中电动汽车相关产品销售额同比增长31%,工业及其他领域增速高达50%。

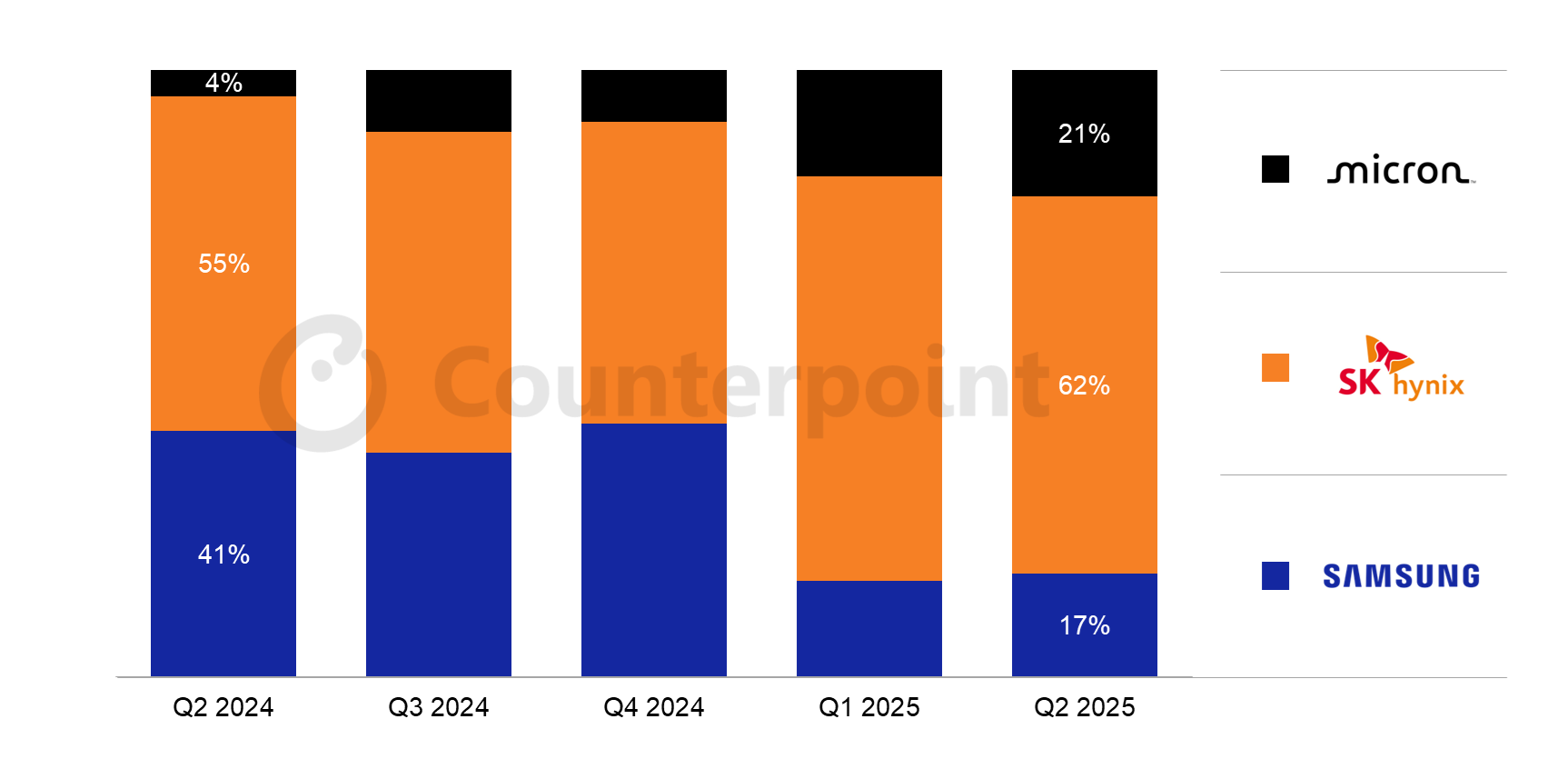

受强劲的人工智能(AI)需求驱动,全球存储芯片市场格局在2025年第二季度迎来历史性转折。韩国SK海力士凭借在高带宽存储器(HBM)领域的领先优势,首次超越三星电子,以21.8万亿韩元的存储业务营收问鼎全球最大存储器制造商。三星同期存储业务营收为21.2万亿韩元,同比下滑3%,退居次席。

8月1日,英伟达官网更新其800V高压直流(HVDC)电源架构关键合作伙伴名录,中国氮化镓(GaN)技术领军企业英诺赛科(Innoscience)赫然在列。英诺赛科将为英伟达革命性的Kyber机架系统提供全链路氮化镓电源解决方案,成为该名单中唯一入选的中国本土供应商。此重大突破性合作直接推动英诺赛科港股股价在消息公布当日一度飙升近64%,市场反响热烈。

全球领先的功率半导体解决方案供应商MPS(Monolithic Power Systems)于7月31日正式公布截至2025年6月30日的第二季度财务报告。数据显示,公司本季度业绩表现亮眼,多项核心指标实现显著增长,并释放出持续向好的发展信号。

贸泽电子(Mouser Electronics)于2025年8月正式推出工业自动化资源中心,为工程技术人员提供前沿技术洞察与解决方案库。该平台整合了控制系统、机器人技术及自动化软件的最新进展,旨在推动制造业向智能化、可持续化方向转型。