发布时间:2011-03-6 阅读量:5722 来源: 发布人:

在应用领域,既要求低成本又要求高性能的实例不在少数,比如:联网手提电脑及其他便携式设备、手机、PDA、机顶盒应用、游戏机以及车载信息娱乐设备等等,不一而足。

消费者不但希望产品功能更强大,也期望便携式产品的电池使用寿命更长。如今,全天候使用已经成为最低要求,为了达到这一要求,电话、智能电话和PDA厂商们必须着眼如何有效率地提升产品性能、增加产品功能。

拿智能电话来说,其性能要求既包括待机时的非活动状态,也包括游戏时的高度活动状态。因此,其系统架构必须能够有效支持产品性能的“两极”。

采用多核处理器架构不但能够解决峰值性能的要求,而且其设计也能够大大降低功耗。多核设备具有性能可扩展性高和功耗低的特点,为设计提供了极大的灵活性。

最新开发的ARM Cortex-A9处理器是ARM处理器系列中性能最高的一款产品,该款处理器采用了广受支持的ARM v7架构,充分实现了其丰富性。Cortex-A9处理器的设计是基于最先进的推测型八级流水线,该流水线具有高效、动态长度、多发射超标量及无序完成特征,这款处理器的性能、功效和功能均达到了前所未有的水平,完全能够满足消费、网络、企业和移动应用等领域尖端产品的要求。

Cortex-A9微架构提供两种选项:可扩展的Cortex-A9 MPCoreTM多核处理器和较为传统的Cortex-A9单核处理器。可扩展的多核处理器和单核处理器(两款不同的独立产品)支持16、32或64KB四路组相联一级缓存的配置,具有无与伦比的灵活性,皆能达到特定应用和市场的要求。

满足多重市场的要求

Cortex- A9处理器为包括手机、高端消费类电子和企业产品在内的多种市场应用提供了一种具有可扩展性的解决方案,因为该款处理器满足了以下各项要求:1. 降低功耗、提升功效和性能;2. 提升峰值性能,适应各种要求最为严苛的应用,开发不同设备时可复用软件和工具;3. 两款Cortex-A9处理器皆具有完美的应用兼容性;4. 媒体处理引擎(MPE)或浮点运算单元(FPU)还能加强特定应用中的性能表现,进一步扩大了这两款处理器的市场应用范围。

两款处理器的应用设计配置均具有极大的灵活性,允许根据具体应用和特定市场的要求进行定制。

先进的微架构

Cortex- A9微架构的设计不但着眼于解决超高频设计的效率低下问题,而且把目标定为在不增加嵌入式设备硅成本的前提下最大限度地提升处理效率。通过综合技术,这种 处理器设计能使设备的时钟频率超过1GHz,而且提供了较高的功效水平,满足了长时间电池供电工作的要求。

流水线性能介绍

Cortex- A9处理器最主要的流水线性能包括以下几条:第一,先进的取指及分支预测处理,可避免因访问指令的延时而影响跳转指令的执行;第二,最多支持四条指令 Cache Line预取挂起,这可进一步减少内存延时的影响,从而促进指令的顺利传输;第三,每个周期内可连续将两至四条指令发送到指令解码,确保充分利用超标量流 水线性能。Fast-loop模式:执行小循环时提供低功耗运行;第四,超标量解码器可在每个周期内完成两条完全指令的解码;第五,支持指令预测执行:通 过将物理寄存器动态地重新命名至虚拟寄存器池来实现。

第六,提升了流水线的利用效率,消除了相邻指令之间的数据依赖性,减少 了中断延时;第七,支持寄存器的虚拟重命名:以一种有效的、基于硬件的循环展开方法,提高了代码执行效率,而不会增加代码大小和功耗水平;第八,四个后续 流水线中的任何一个均可从发射队列中选择执行指令—提供了无序分配,进一步提高了流水线利用效率,无需借助于开发者或编译器指令调度。确保专为上一代处理 器进行优化的代码能够发挥最大性能,也维护了现有软件投资。

第九,每周期支持两个算术流水线、加载-存储(load- store)或计算引擎以及分支跳转的并行执行;第十,可将有相关性load-store指令提前传送至内存系统进行快速处理,进一步减少了流水线暂停, 大幅提高了涉及存取复杂数据结构或C++函数的高级代码的执行效率;第十一,支持四个数据Cache Line的填充请求:而且还能通过自动或用户控制预取操作,保证了关键数据的可用性,从而进一步减少了内存延时导致的暂停现象;第十二,支持无序指令完成 回写:允许释放流水线资源,无需受限于系统提供所需数据的顺序。

Cortex-A9 MPCore技术

Cortex-A9 MPCore多核处理器是一种设计定制型处理器,以集成缓存一致的方式支持1到4个CPU内核。可单独配置各处理器,设定其缓存大小以及是否支持FPU、 MPE或PTM接口等。此外,无论采用何种配置,处理器都可应用一致性加速口,允许其他无缓冲的系统控制外设及加速器(如DMA引擎或加密加速器)核与一 级处理器缓存保持缓存一致。另外还集成了一种符合GIC架构的综合中断及通信系统,该系统配有专用外设,其性能和软件可移植性都更上一层楼,适当配置后, 可支持0(legacy bypass 模式)到224个独立中断资源。这种处理器可支持单个或两个64位AMBA3 AXITM互联接口。

Cortex-A9 MPCore多核处理器采用了通过硅验证的ARM MPCore技术的增强版,实现了可扩展型多核处理:

侦测控制单元(SCU)

SCU 是ARM多核技术的中央情报局,负责为支持MPCore技术的处理器提供互联、仲裁、通信、缓存间及系统内存传输、缓存一致性及其他多核功能的管理。同 时,Cortex-A9 MPCore处理器还率先向其他系统加速器及无缓冲的DM A驱动控制外设开启此类功能,通过处理器缓存层次的共享,有效地提高了性能、减少了整个系统的功耗水平。不仅如此,利用这种系统来维持每个操作系统驱动中 的软件一致性,软件复杂性就大大降低了。

加速器链接埠

这个与AMBA 3 AXI兼容的Slave接口位于SCU之上,为多种系统Master接口提供了一个互联接口;出于总体系统性能、功耗或软件简化等方面的考虑,最好直接将 这些Master接口与Cor tex-A9 MPCore处理器相连。这是个标准的AMBA 3 AXI Slave接口,支持所有标准读写事务,对所接部件无任何附加一致性要求。

然而,指向某个一致内存区的读取事务要与SCU发生作用,以检测所需信息是否已经存储在处理器的一级缓存之中。若检 测出确已存储,相应信息将被直接返回给发出请求的组件。如果一级缓存中不存在该信息,在最终传给主内存之前也可能检测二级缓存。对于指向一致内存区的写入 事务,SCU会在把写入事务传送至内存系统之前强制确保一致性。也可选择性地将事务分配给二级缓存,以避免直接写入片外内存所带来的功耗及性能影响。

通用中断控制器(GIC)

该 GIC采用了最近标准化和架构的中断控制器,为处理器间通信及系统中断的路由选择及优先级的确定提供了一种丰富而灵活的解决办法。最多支持224个独立中 断,通过软件控制,可在整个CPU中对每个中断进行分配、确定其硬件优先级并在操作系统与信任区软件管理层之间进行路由。这种路由灵活性加上对中断虚拟进 入操作系统的支持,是进一步提升基于半虚拟化管理器解决方案功能的关键因素之一。

先进的总线接口单元

Cortex-A9 MPCore处理器增强了处理器与系统互联之间的接口性能,其先进特色功能最大限度地提高了系统性能,为各种系统集成芯片设计理念创造了更大的灵活性。

这 种处理器支持单个或两个64-b i t AMBA 3 AXI Master接口的设计配置,可以按CPU的速度全负荷地将事务传送至系统互联之中,最高速度可达12G B/s以上。另外,第二接口也可定义某种事务过滤,只处理全局地址空间的一部分;也就是说,可在处理器内部直接对地址空间进行切分,进一步加强了系统设计 的灵活性。

而且每个接口还支持不同的CPU-总线频率比(包括同步半时钟比),不但提高了设计灵活性,而且为需要考虑DVFS或高速集成内存的设计增加了系统带宽。同时为完整的A RM智能能量管理 (IEM)功能提供了良好的支持。

特定应用的计算引擎加速

处理器不但拥有优化的标准架构特色,而且还可增加以下任一设计功能:

先进二级缓存控制器:ARM二级缓存控制器(PrimeCell PL310)与Cortex-A9系列处理器同步设计,旨在提供一种能匹配Cortex-A9处理器性能和吞吐能力的优化二级缓存控制器。

.jpg) |

| 最新开发的ARM Cortex-A9处理器采用了广受支持的ARM v7架构,处理器性能、功效和功能均达到了前所未有的水平,完全能够满足消费、网络、企业和移动应用等领域尖端产品的要求。。 |

PL310最多可为每个接口提供8项AXI事务支持,支持按Master接口进行锁定;这样一来,即通过将PL310用作加速器与处理器之间的缓冲器,充分利用一致性加速口,实现多个CPU或组件之间的可控共享,既提升了系统性能,也降低了相关功耗水平。

另外,PL310不但具有Cortex-A9先进总线接口单元的各项功能,支持同步1/2时钟比,有助于减少高速处理器设计中的延时现象,而且能够对第二MasterAXI 接口设置地址过滤,分割地址和频率域、以及集成片上内存的快速存取提供了支持。

PL310最高可支持2 M B的四至十六路组相联二级缓存,可与奇偶校验及支持E C C的R A M集成,而且运行速率能够与处理器保持一致。而先进的锁定技术也提供了必要的机制,从而将缓存用作相关性加速器和处理器之间的传输RAM。

Cortex-A9 程序跟踪宏单元(PTM):Cortex-A9 PTM为两款Cortex-A9处理器提供了兼容ARM CoreSight技术的程序流跟踪功能,能够对处理器中的实际指令流实现完全可视化的管理。Cortex-A9 PTM通过周期计数实施性能分析,可对所有代码分支和程序流变动进行跟踪管理。

另外提供Cortex-A9 CoreSight设计套件,可使来自多个处理器的跟踪流具备相关性,而且包括跟踪和调试Cortex-A9 MPCore多处理器设计所需要的全部CoreSight组件。

综合灵活性和参考方法

Cortex- A9处理器充分发挥了综合性设计流程的灵活性,其相关产品能够应用于任何代工厂和工艺节点。通过与各大EDA公司开展持续合作,ARM制定了专门的“实现 参考方法”(iRM),使Cortex-A9处理器的授权客户能够根据所选工艺技术对处理器进行定制、实现、验证和差异化处理。这些参考方法结合了逻辑和 物理综合技术,提供了一条可预测的硅技术之路,构成了定制方法开发的基础。此外,iRM还可整合ARM Artisan前端库文件以及经过预编译的RAM,增强了iR M实现处理器实施工艺的能力,在完整性上远远超过了已有参考解决方案。

开发工具与生态系统

所有ARM处理器都拥有ARM RealView开发工具套装、多种第三方工具、操作系统和EDA厂商的支持。

ARM RealView工具拥有独特的功能,其所提供的解决方案涵盖从概念化到最终产品的整个开发过程。RealView套装中的每种工具都与ARM硬件和软件 IP协同开发,为IP发挥最佳性能提供了保障。没有其他供应商能够为ARM IP提供这种涵盖系统、处理器设计和软件开发全部过程的独特端对端工具链支持。

通过ARM RealView套装提供的多种既相互独立又相互联系的工具,构架设计师和开发人员完全可以满怀信心地、以前所未有的速度将优质产品投放市场。

第三方支持

ARM 合作伙伴联盟是业界规模最大的合作伙伴网络,由领先的硅、系统、设计支持、软件和培训服务供应商组成。通过这个网络,系统设计师可以获得大量ARM 技术和优化IP,并为基于A R M架构的产品提供了一个涵盖设计、制造和最终应用等过程的完整解决方案。有关详情,可访问http://www.arm.com/community。

物理IP

ARM 的Artisan物理IP产品的设计目的是在性能、密度、功耗和特定制造工艺的产量之间达最佳平衡。产品涵盖各种45-250纳米工艺,同时提供多种格式 和模型,并为业界主要的EDA工具提供了支持。ARM Artisan IP平台及产品组合提供了多种选择,完全能够满足系统集成(SoC)设计师的需求。

AMBA

AMBA互联总线协议构成了集成互联规范(起到集成设计框架的作用)实际行业标准的基础, 有效提供了将各个IP组件粘接起来的‘数字胶水’。同时也是ARM 设计可复用战略的主干。

通 过更广范围的系统集成商的支持,ARM将竭力提供业界技术最先进、支持最完善且免费的互联规范。目前,外设 IP的PrimeCell组合支持AMBA协议的第2和第3版发表的协议,该协议定义了AMBA AXITM、AHBTM、AHB-Lite、APB和ATB规范。

完整的系统解决方案

两款ARM Cortex-A9处理器都包含ARM特定应用架构扩展集,包括DSP和SIMD扩展集和Jazelle® 技术、TrustZone和智能功耗管理(IEM™)技术。此外,ARM已开发一整套支持新处理器的技术,以缩短设计时间并加快产品上市时间。这一完整的系统解决方案包括:

• 浮点单元(FPU):Cortex-A9 FPU提供高性能的单精度和双精度浮点指令。

• 媒体处理:Cortex-A9 NEON媒体处理引擎(MPE)提供了Cortex-A9 FPU所具有的性能和功能,以及在Cortex-A8处理器中首次推出的用于加速媒体和信号处理功能的ARM NEON 先进 SIMD指令集。

• 物理IP:提供在Cortex-A9处理器上实现低功耗、高性能应用所需的众多标准单元库和存储器。标准单元包括功耗管理工具包,可实现动态和漏泄功耗节省技术,例如时钟门控、多电压岛和功率门控。还提供具有先进的功耗节省功能的存储编译器。

• Fabric IP:Cortex-A9处理器得到广泛的 PrimeCell® fabric IP元件的支持。这些元件包括:一个动态存储控制器、一个静态存储控制器、一个AMBA® 3 AXI可配置的内部互连及一个优化的L2 Cache 控制器,用于匹配Cortex-A9处理器在高频设计中的性能和吞吐能力。

• 图形加速: ARM Mali™ 图形处理单元及Cortex-A9处理器的组合,将使得SoC合作活动能够创造高度整合的系统级解决方案,带来最佳的尺寸、性能和系统带宽优势。

• 系统设计:ARM RealView® SoC Designer工具提供快速的架构优化和性能分析,并允许在硬件完成以前很长时间即可进行软件驱动程序和对时间要求很严格的代码的早期开发。 RealView系统发生器(RealView System Generator)工具为基于Cortex-A9处理器的虚拟平台的采用提供超快建模能力。Realview工具中关于Cortex-A9处理器的基于周期的(cycle based)及程序员视角的模型将于2008年第二季度上市。

• 调试: ARM CoreSight™片上技术加速了复杂调试的时间,缩短了上市时间。程序追踪宏单元技术(Program Trace Macrocell technology)具有程序流追踪能力,能够将处理器的指令流完全可视化,同时配置与ARMv7架构兼容的调试接口,实现工具标准化和更高的调试性能。用于Cortex-A9处理器的CoreSight设计工具包扩展了其调试和追踪能力,以涵盖整个片上系统,包括多个ARM处理器、DSP以及智能外设。

• 软件开发:ARM RealView开发套件(ARM RealView Development Suite)包括先进的代码生成工具,为Cortex-A9处理器提供卓越的性能和无以比拟的代码密度。这套工具还支持矢量编译,用于NEON媒体和信号处理扩展集,使得开发者无需使用独立的DSP,从而降低产品和项目成本。包括先进的交叉触发在内的Cortex-A9 MPCore多核处理器调试得到RealView ICE和Trace产品的支持,同时也得到一系列硬件开发板的支持,用于FPGA系统原型设计和软件开发。

40nm版(台积电)

ARM Cortex-A9 ,基于台积电的40nm-G制造工艺,已经开发出两款Cortex-A9微架构双核处理器设计方案,分别对应高性能和低能耗。其高性能版本将把ARM处理器的频率上限提高到2GHz以上。

ARM的Cortex系列处理器设计近来在移动市场大行其道,包括iPhone 3GS、Palm Pre以及频率高达1GHz的东芝TG-01等最新顶级智能手机实际上都是基于Coretex-A8核心,而近来发展方兴未艾的Smartbook智能本基本上也都是这一架构处理器的应用产品。

Cortex-A9将继续这一路线,由于从Cortex-A8普遍使用的65nm工艺升级到40nm,Cortex-A9高性能版本将在使用双核心的同时,把频率拉高到2GHz以上,同时依然保持超低功耗,预计高性能Smartbook将是它的主要战场。

低功耗版本方面,主要面向机顶盒、数字电视、打印机及其他应用,运算能力可达4000DMIPS,同时功耗不足0.25W。

和Cortex-A8一样,ARM将把该核心设计授权给多家厂商进行再开发和制造,包括德州仪器、Broadcom、高通、三星等ARM授权厂商预计从今年第四季度开始就将推出该架构的处理器产品。

28nm版(GlobalFoundries)

GlobalFoundries成功流片了基于ARM Cortex-A9双核心处理器的技术质量检验装置(TQV),而且第一家使用了28nm HP高性能工艺、HKMG(高K金属栅极)技术。

28nm与40nm的比较

GF透露,这次TQV是今年八月份在位于德国德累斯顿的Fab 1晶圆厂内完成的,使用了一整套优化的ARM Cortex-A9物理IP,能从每一个方面模拟真正的SoC产品,从而实现最大程度的频率分析、缩短产品设计周期的时间,还有完整的可测性设计 (DFT)。据透露,新处理器的工作频率在2.0-2.5GHz之间,比上代40nm工艺版本快了500MHz左右,性能也有明显提升。

GF、ARM估计,相比于40nm工艺,新的28nm工艺制造平台能带来40%的计算性能提升、30%的功耗下降、100%的待机电池续航能力提升。

这也是GF、ARM去年十月宣布的战略合作的一部分。GF预计今年年底拿出新处理器的实际样品。

顺便说一句,ARM处理器可能会让很多人感到陌生而遥远,但实际上我们身边到处都是它的影子,目前全球使用量估计高达200亿颗,占全部嵌入式32位RISC处理器的90%之多。

双核Orion(三星)

三星公布了基于Cortex-A9架构的全新双核处理器,这或许也是首款真正意义上的双核手机处理器。先不问它的主频如何如何高,三星官方对这款新处理器的描述,说了个细节:3D运算处理提升五倍!

不过,这款名叫Orion的处理器,主频仍然为1GHz,远没有之前传言的 2.0-2.5GHz那样强大(2.0-2.5GHz应该是指诸如平板电脑这种移动终端设备)。并且工艺是45NM的,虽然比起Cortex-A8的 60NM有提高,但仍没达到GlobalFoundries前两天Cortex-A9的28NM(不过28NM工艺的手机处理器,迟早的事)。 由于这款处理器是双核的,想必未来若运用到手机上,在多任务处理上,提升也会很大的。同时,这颗双核处理器还将支持1080p全高清视频解码能力,且能通过HDMI接口同时对3个屏幕进行视频输出。

目前,Cortex-A8被广泛运用到高端旗舰手机上面。诸如iPhone 4、i9000、3GS和Milestone等强机,均是采用的此构架的处理器,其性能,用过的也都知道它的强大。

至于Cortex-A9什么时候正式上市,据三星官方称,这颗基于Cortex-A9架构的双核处理器将于2011年上半年正式投产。

飞思卡尔iMX515

主频为800MHz,目前还到不了1GHz,采用该方案的山寨平板样机已经可以在市场上看到,内存可支持到512M,最高视频输出为720P。这样的硬件平台和Android2.2配合起来才比较理想。

三星C100/C110

基于ARM Cortex-A8内核,主频在1GHz,512M内存,可以直接上Android2.2,性能超强,据说iPad里面的A4处理器,都是三星设计和代工,苹果虽然不承认,但三星芯片的强大大家都是知道的。不说iPad,魅族手机被称为最像iPhone的手机,它的下一代M9手机,就是采用三星C110 芯片。

Nvidia Tegra 2

一直以来,Tegra都是非常让人期待的,就是外面吹的挺响,不见产品出来。现在终于有眉目了,万利达即将上市的一款ZPad,就准备采用Tegra 2芯片。Tegra 2性能很强劲,内建ARM双核Cortex A9处理器,主频到1GHz,最高支持1GB内存,支持1080P的全高清视频播放,多媒体方面增加了对Flash 10的支持,3D性能是Nvidia的强项就不用多说。不过大家要做好心理准备,Nvidia的东西是不会太便宜,估计终端的品牌价格会达到3K。

本文小结

Cortex-A9和Cortex-A9 MPCore是ARM处理器家族中的两个新成员,旨在满足单核和多核处理器设计需求。两款产品采用了相同的微架构,整合了多种特色功能,使处理器核心和整个集成系统的架构功能、性能和功效得到了大幅提升。

单 核处理器比现有ARM11级设备提供了更好的性能和功效,不但增强了移动设计的功能,而且降低了功耗水平,延长了电池使用寿命。而在实现方面,这款处理器 还具有出色的架构软件兼容性,能够在达到Cortex-A8级性能的前提下降低成本,从而扩大了相关软件投资的市场应用范围。

而MPCore型处理器则拥有先进的电源管理功能,能够进一步降低功耗,达到并超过了日益增多的市场和应用对功耗的要求。除此之外,Cortex-A9 MPCore还拥有卓绝的性能可扩展性,将 A RM 处理器设计中浑然天成的功效特性奉献给了更多的市场领域。

全部配套技术专门针对两款Cortex-A9处理器而设计,能够很好地满足特定应用和市场所要求的性能,尤其是无线、娱乐、成像及其他高端多媒体应用。

全球领先的传感器与功率IC解决方案供应商Allegro MicroSystems(纳斯达克:ALGM)于7月31日披露截至2025年6月27日的2025财年第一季度财务报告。数据显示,公司当季实现营业收入2.03亿美元,较去年同期大幅提升22%,创下历史同期新高。业绩增长主要源于电动汽车和工业两大核心板块的强劲需求,其中电动汽车相关产品销售额同比增长31%,工业及其他领域增速高达50%。

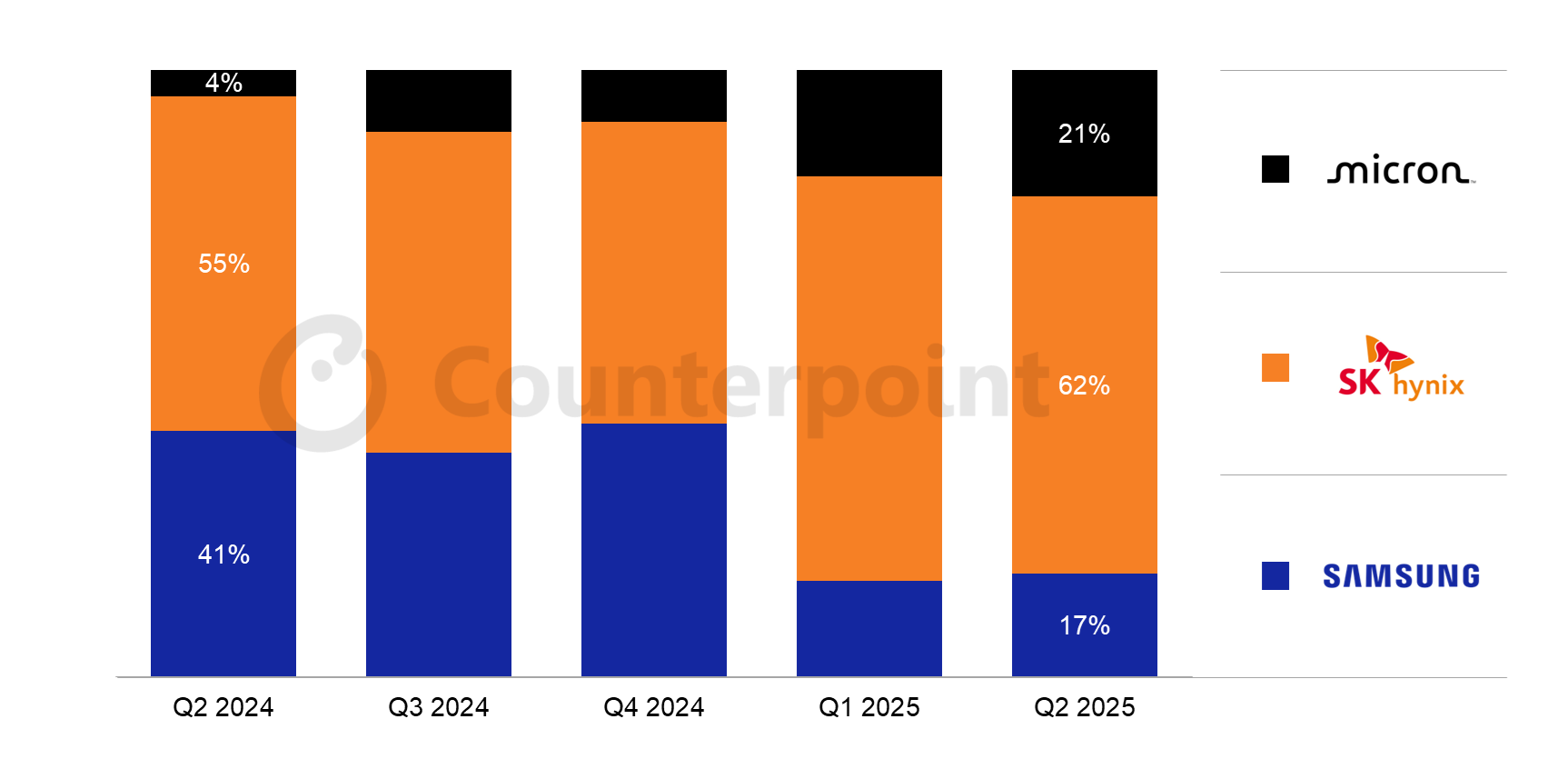

受强劲的人工智能(AI)需求驱动,全球存储芯片市场格局在2025年第二季度迎来历史性转折。韩国SK海力士凭借在高带宽存储器(HBM)领域的领先优势,首次超越三星电子,以21.8万亿韩元的存储业务营收问鼎全球最大存储器制造商。三星同期存储业务营收为21.2万亿韩元,同比下滑3%,退居次席。

8月1日,英伟达官网更新其800V高压直流(HVDC)电源架构关键合作伙伴名录,中国氮化镓(GaN)技术领军企业英诺赛科(Innoscience)赫然在列。英诺赛科将为英伟达革命性的Kyber机架系统提供全链路氮化镓电源解决方案,成为该名单中唯一入选的中国本土供应商。此重大突破性合作直接推动英诺赛科港股股价在消息公布当日一度飙升近64%,市场反响热烈。

全球领先的功率半导体解决方案供应商MPS(Monolithic Power Systems)于7月31日正式公布截至2025年6月30日的第二季度财务报告。数据显示,公司本季度业绩表现亮眼,多项核心指标实现显著增长,并释放出持续向好的发展信号。

贸泽电子(Mouser Electronics)于2025年8月正式推出工业自动化资源中心,为工程技术人员提供前沿技术洞察与解决方案库。该平台整合了控制系统、机器人技术及自动化软件的最新进展,旨在推动制造业向智能化、可持续化方向转型。