发布时间:2010-12-27 阅读量:1377 来源: 发布人:

【中心议题】

【解决方案】

聚合物薄膜场效应晶体管在结构设计上继承了金属-氧化物-半导体场效应晶体管(MOSFET)的体系结构,主要由三部分组成,包括源、漏、栅三个电极,绝缘层和半导体层。器件结构广泛采用顶接触型、底接触型和顶栅结构三种类型,其结构示意图如图所示。

.jpg)

据Roichman等人报道,对于同一种聚合物半导体,顶接触型器件的特性往往比底接触型器件的更优越,这是因为顶接触型的注入面积比底接触型的注入面积大,引起电极与半导体层之间的接触电阻减小所致。由于有机PFET器件一般不采用传统的光刻工艺制造,器件的沟道长度相对较长,为了增大其输出电流,往往把源、漏电极作成梳状结构,以增加宽长比,从而增加了器件的占用面积,这显然不利于器件的集成。因此,短沟道PFET器件的制备技术就成为制造技术的关键。下面介绍PFET器件的制备工序和技术。

1选取衬底

目前可用作短沟道PFET器件衬底的材料主要有硅单晶、玻璃和塑料等,应根据器件的应用领域来选取。单晶硅为高掺杂的n型或p型材料,用单晶硅作衬底时,衬底也作为器件的栅极,此时绝缘层大多采用SiO2、Si3N4、Al2O3等无机材料,以减小器件的漏电流。用玻璃作衬底时,通常在玻璃上沉积一层ITO作为栅极,绝缘层可以是无机材料也可以是有机材料。用塑料作衬底,主要是为了制备全柔性有机电子器件。

2制备绝缘层薄膜

绝缘层薄膜的制备方法根据所选用的绝缘层材料不同而不同。对于SiO2、Si3N4、Ta2O5等无机绝缘膜,可以采用金属有机物化学汽相沉积(MOCVD)法、电子束蒸发法和热氧化法等;对于PVP、PMMA、P4VP等有机绝缘膜,大都采用最简单的溶液旋涂法。对于同种聚合物半导体膜,器件结构相同而绝缘层材料不同时,器件特性不同。Podzorov等人用规整的聚3-已基噻吩(RR-P3HT)作为有机半导体层,采用浸泡涂覆(dip coating)工艺制备了绝缘层不同的器件,并对它们进行了比较,结果发现,采用Al2O3/SiO2双层绝缘层的器件具有更高的场迁移率和开关电流比。Facchetti等人综合报道了采用各种栅绝缘介质层的有机场效应晶体管器件的性能。

3制备聚合物半导体膜

在PFET中,半导体活性层材料一般选用可溶性聚合物,采用溶液相成膜工艺完成薄膜沉积。其中最为流行的成膜工艺是旋转涂敷,它类似于硅平面工艺中的甩胶工艺,在基片启动时,快速滴入待成膜的聚合物溶液,当基片高速旋转时,该溶液在基片上立刻散布成均匀膜。当溶剂蒸发后,基底上就形成了固态薄膜。有机薄膜的性能,如:有序化程度和晶粒大小,直接影响PFET的器件性能。目前,这方面的研究主要集中在:(1)通过一些后处理工序(如:热处理)来提高薄膜中分子结构的有序度、增加薄膜中晶粒的大小,从而有效地改善PFET的器件性能。(2)溶剂种类对成膜质量也有较大的影响,选择相容性好的溶剂有利于改善成膜质量。(3)有机半导体聚合物的纯度也是重要因素,通过优化有机半导体聚合物的合成工艺来提高聚合物纯度。(4)通过优化旋涂工艺,如:旋涂前基片的表面处理方法、基片旋转速度及薄膜厚度控制等,来改善成膜质量。除了旋转涂敷工艺外,近来还发展了其它更简单的溶液成膜工艺,如:浸泡涂覆(dip coating)和旋转涂敷(spin-casting)等,Wang等人报道了基片从溶液中抽取速度不同对成膜质量和器件性能的影响。

4图形加工技术

图形加工技术是PFET器件制备中最重要的工序之一,它决定器件的最后结构。器件结构直接关系到器件的整体性能,如开关速度大小、饱和区电流大小、栅电容大小等参数。为了满足器件应用的需要,器件的源、漏、栅电极的图形和尺寸需要通过图形加工技术来实现。比如,源、漏之间的间距(沟道长度)越小,PFET的输出电流就越大,开关速度就越高。另外,为了消除寄生漏电容和减小串扰现象,聚合物半导体要求限制在沟道区域内以获得更好的器件性能,这也是通过图形加工来实现。下面介绍几种典型的图形加工技术:

(1)掩膜版直接图形转换技术这是一种广泛采用的方法,即首先在某种特殊材料上准确地加工出源、漏电极图形,在源、漏电极制备前,将其作为掩膜版紧贴基片,电极材料通过蒸镀或溅射方法可在基片上形成电极图形。此方法适合于金属电极、小分子有机物作为电极或半导体层,而不适用于聚合物作为电极或半导体层。

(2)印戳(Stamp)印刷技术也称为软平版印刷技术,该技术用一块厚橡胶板用作印戳,用通常的光刻工艺在该橡胶板上蚀刻源电极和漏电极的线路图形,然后用某种有机化合物湿润印戳,其间在待印刷的线路图形的基底上蒸发一层薄金膜。在印戳印刷时,印戳上的有机化合物分子被粘结到金膜,形成自组装单分子层,再用特殊蚀刻剂腐蚀未被自组装单分子层保护的金膜,接着再用另一种化学溶剂溶解自组装层,而保留了印刷的源、漏电极图形。此方法形成图形的分辨率较低,限制在10μm。如果用耐磨损的钢制印戳代替橡胶,可使线路图形的分辨率达到纳米级水平,称为纳米压印平板印刷工艺,被认为是目前有机电子学或聚合物电子学最有发展前途的制造方法,可使塑料芯片的集成度大幅度提高。

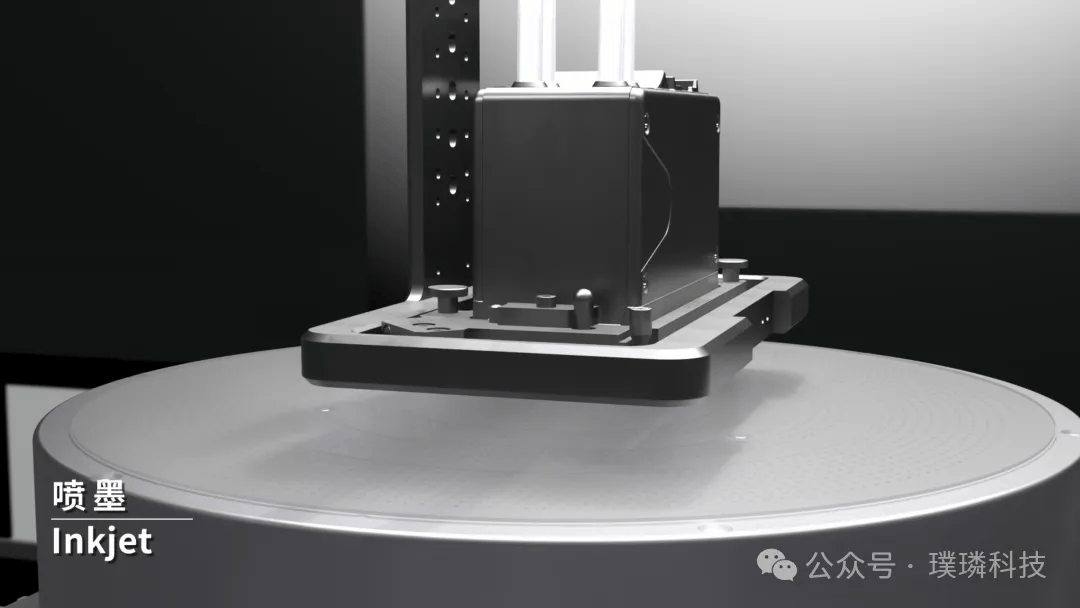

(3)喷墨打印技术类似于计算机所用的喷墨打印机,是将墨滴从小孔中直接喷射到介质的指定位置而形成图像的一种非接触点阵加工技术。该技术特别适应于全有机PFET器件的制作,其原因如下:不同材料可以从不同喷嘴同时喷出;喷头相对于先前沉积的图形可以局部对准,因此能够提供在大面积上精确定位;对于专用线路,可以在预制的晶体管栅极陈列上简单地喷墨打印互连线和孔穴通道构建的网络;该工艺在PFET器件制备中用于制作源、漏电极,互连线和栅电极,其工艺流程大致为:首先用喷墨打印将导电聚合物印刷到基底上,并制成源电极和漏电极以及互连线;然后用旋转涂敷工艺沉积半导体聚合物,形成有源半导体层,以及制作聚合物栅介质层;最后用喷墨打印导电聚合物栅电极。

激光烧蚀技术该技术是在已沉积聚合物的基底上通过激光局部照射,使其熔解挥发,从而形成加工图形。这是一种干法蚀刻技术,避免了溶剂对底层有机层的损伤而降低器件的性能。

在USB4®和Thunderbolt™接口传输速率突破10GHz的产业背景下,静电放电(ESD)和意外短路引发的系统失效已成为消费电子与通信设备的核心痛点。传统保护方案在射频性能与防护强度间的取舍矛盾,特别是不合规Type-C接口中Vbus与TX/RX短路风险,迫使行业寻求突破性解决方案。Nexperia最新推出的五款1V保护二极管,通过创新架构实现鱼与熊掌兼得的技术跨越。

2025年8月1日,璞璘科技自主研发的首台PL-SR系列喷墨步进式纳米压印设备正式通过验收并交付国内特色工艺客户。该设备攻克了步进硬板非真空贴合、喷胶与薄胶压印、压印胶残余层控制等关键技术,标志着我国在高端半导体装备领域取得实质性突破。

全球晶圆代工龙头企业台积电在推进2nm先进制程量产的关键阶段,于内部安全审查中发现异常活动。公司声明显示,其监控系统侦测到未经授权的技术信息访问行为,已对涉事人员解除雇佣关系,并启动法律程序追责。

在2025年8月4日,全球领先的半导体解决方案供应商Onsemi正式发布了其2025年第二季度财务报告。本季度,公司展现了稳健的经营表现,反映其在功率半导体领域的战略优势。随着汽车电子化和人工智能应用的加速渗透,Onsemi通过持续优化业务模式,在充满变化的市场环境中取得可喜进展。

据Counterpoint Research近期发布的报告,2025年第二季度,全球智能手机市场呈现显著收入增长,总收入达1000亿美元以上,同比提升10%。这一数据创下了自统计以来第二季度的收入新高峰。尽管出货量仅同比增长3%,不足总量的显著跃升,但市场动能源于平均售价(ASP)的大幅上涨。报告显示,本季度ASP同比增长7%,达到约350美元的历史高位,反映出消费者对高端设备的强劲需求推动了整体盈利能力提升。这种收入与出货量的差异化增长,突显了市场结构正加速向高端化转变。