发布时间:2010-11-14 阅读量:1002 来源: 我爱方案网 作者:

视额应用中对压缩,减少数据量或者数据传输率的要求可以归纳为以下两种基本要求:

1),在已存在的基础中加入新的功能。彩色电视就是一个好例宁。它面临的挑战就是将附加 信息(色彩)整合进已存在的黑白信号中。

2),经济利益。在通信领域,数据链接的花费通常是与数据传输串成正比的。因此,压缩系 数越高,花费就越低。同时,减少的存储花费构成了压缩技术经济上的另一个优势。

色度亚采样的进一步知识

对表示色度的色差信号进行亚采样经常用于减少数据密度,4:2:2是—个明显的例子.它充分利用了人眼对于亮度变化的敏感程度要强于色度变化这一特点。在减少带宽的努力中这已 经不是新核念了。它最初的应用要回顾到1950年代早期的NTSC和PAl复合信号标标准。在这 些复合信号标准体系中,两个色差倍号的分辨串带宽被减少到大约1MHz。类似的带宽降低 方法也被皮用到一些早期的数字效果单元上。这些设备使用4:1:1的采样格式,其中采样仍 是共结点的,但色差信号的采样频串只是亮度信号的四分之一。 垂直亚采样可以达到与4:1:1相同的降低色度数据密度的效果,这时的目标就是沿水平和垂 直方向把色度分辨串降低相同的数量。在4:2:0的采样中,来自一场中相临两条扫描线的色 度采样经内插处理,生成一个单独的色度采样,它在空间上位于原始采样之一和相反场中对 应扫描线上相应位置的正中。所谓对应扫描线是指,相反场中,在空间上位于当前场 中被采样的两条扫描线之间的那条扫细线。图3中的实心箭头搀出扫描线n和n+2的采样经 过内插处理生成了位于扫描线0和n+1之间的新采样。 ’ 4:2:0采样有许多的缺点。首先,由于使用隔行扫描已经损失了垂直分辨率,其次,色度采 样的垂直内插很复杂,还要求自适应滤波,达经常导致图象质量没有4:1:1的令人满意,多 代(multi-generation)性能不佳,最后,利用垂直亚采样在水乎和垂直两个方向上同等程 度地降低色度分辨串这一想法本身就有其根本性的缺陷:它并未考虑在水平和垂直两个方向 上采样密度的差异。表1总结了这些针对不同视频格式的采样密度,包括NTSC和PAL.

如果目的是最终使用诸如NTSC和PAL的复合信号标淮来传送信号,那么4:2:0是最糟 糕的可能选项。

显而易见,4:2:O并没有在两个方向上同等程度地降低色度分辨率.注意到水乎分辨率和垂 直分辨率3:1的比例就很容易得出这个结论。即使在引入4:3的长宽比之后,水平垂直分 辨串的比值仍是2.25:1。显然,4:1:1的采样结构更能够在两个方向上提供平衡的分辨率. 如果目的是最终使用诸如NTSC或PAL的复合信号标准来传送信号,那么4:2:0是最糟糕的 可能选项。它提供比NTSC或PAL都要高的水平分辨率,因此它提供的垂直色度分辨率比这 些复合信号标准所提供的要差得多。4:2:0的使用对水平和垂直色度分辨率都将造成损伤.

压缩过程

压缩基本上是这样一个过程:通过消除存在于视频信号里的冗余成分,来减少图象或图象组 的内容信息。概括地说,压缩技术就是试图识别冗余内容,再从比特流中除去大量的此类成 分。

用DCT识别冗余

对于许多压缩系统,第一步工作就是识别存在于视频信号的每帧每场中的空间冗余,这是通 过对整幅图象做DCT(离散余弦变换)来完成的。DCT是一个无损的,可逆的数学过程,它把 空间幅度数据转化为空间频率数据。在用于视频压缩时,这一运算过程是以亮度采样和相应 的色差采样构成的8*8点的块为单位进行的。(图4)左上角的DCT系数反映块的DC(直 流)分量,位于既分量下方的系数代表着逐渐增高的垂直空间领率,位于DC分量右侧的系 数代表看逐渐增高的水平空间频率,其他系数则代表垂直水平空间频串的不同组合。 由于视频图象的自然属性,DCT变换经常使代表较高空间频率的DCT系数的值很小。类似的, 由于人类视觉分辨串的特点,许多非零,代表较高空间频率的可以很粗糙地定义(也就是用 较少的比特来表达)或完全弃之不用,也不会引起明显的图象劣化。DCT变换并不能减少数 据量,事实上,为了达到可逆和无损,必须使用更多的有效比特(有效数字)来确保计算过 程中没有进位错误。

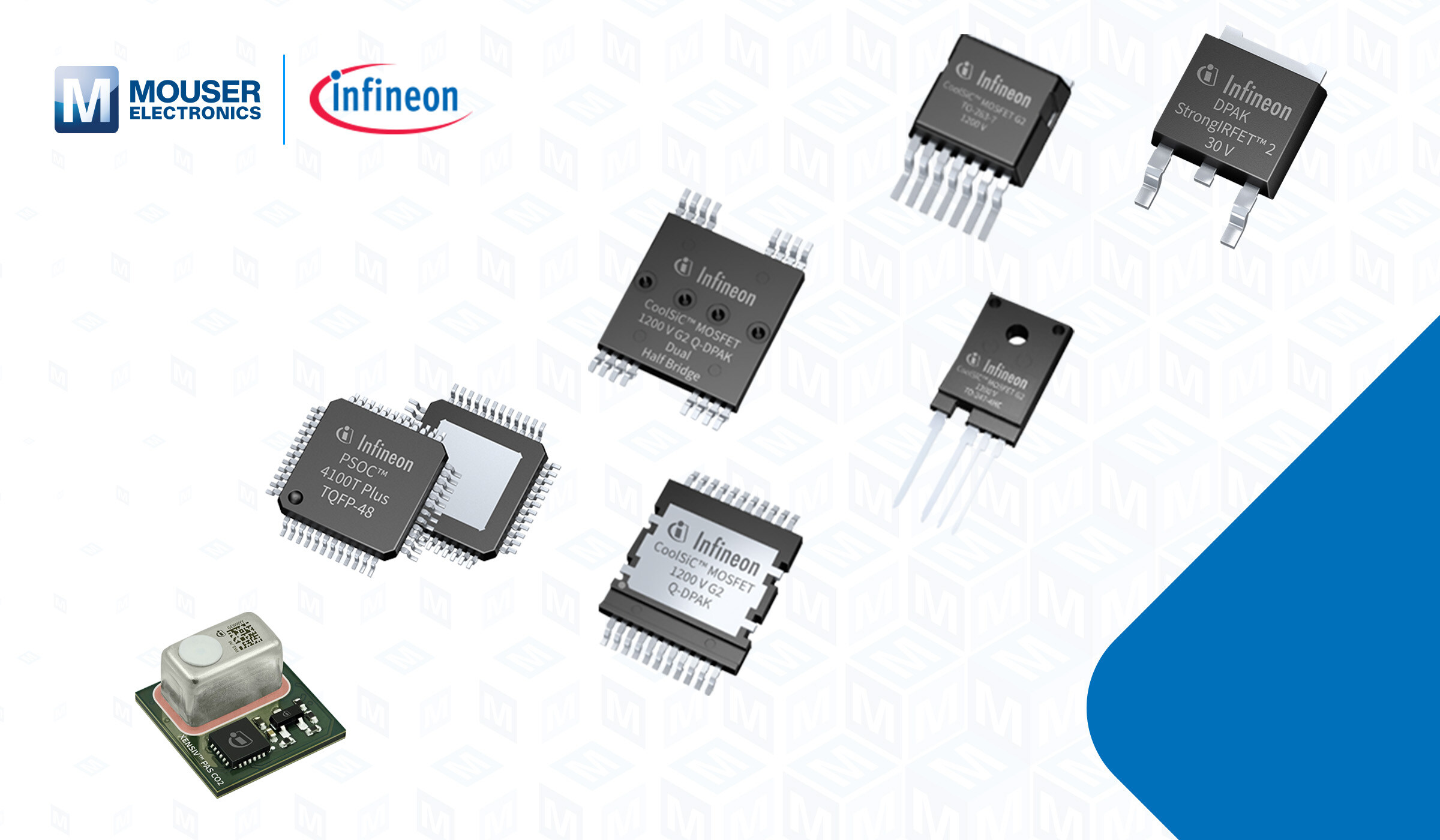

英飞凌XENSIV™ PAS CO2 5V传感器可持续提供高质量数据,并且满足WELL™建筑标准的性能要求。

英伟达否认H100和H200售罄传闻

红外传感器是一种利用红外线进行检测的电子设备,广泛应用于工业自动化,安防监控,智能家居,医疗设备等领域

随着全球制造业迈向集成化与数字化,独立机器人单元正逐渐融入更广泛的自动化系统。DigiKey 本季发布的《机器人技术探秘》的第 5 季《未来工厂》视频系列,联合行业领先企业 Eaton 和 SICK,系统解析了从电气控制、传感技术到数据互联等多个层面的前沿解决方案。新一季邀请了多名专家,一起探讨支撑现代机器人制造与自动化的基础设施与创新技术。

SEMI-e深圳国际半导体展暨2025集成电路产业创新展将于2025年9月10日至12日在深圳国际会展中心(宝安新馆)隆重开幕。本届展会由CIOE中国光博会与集成电路创新联盟联合主办,中新材会展与爱集微共同承办,以“IC设计与应用”、“IC制造与供应链”及“化合物半导体”为核心主题,系统覆盖集成电路全产业链环节。