发布时间:2010-10-17 阅读量:1116 来源: 发布人:

设计单个电源

在电源设计流程的最初阶段,工程师首先要确定电压与电流规格,包括最低与最高输入电压、输出电压及负载电流。用户必须针对组件大小、效率及成本,确定整体设计目标。然后,设计师可以使用美国国家半导体 WEBENCH® 设计工具的可视化功能来获得最符合设计要求的解决方案。

如图 1 显示,输入为 14至22V,输出为 3.3V、1A 典型降压电源的不同解决方案。y 轴表示组件大小,x 轴表示效率,圆圈大小表示物料总成本。在此案例中,显示了一组在输入下可能获得的 50 种不同设计,而不同设计之间的性能存在很大差异。这是由于:A) 开关频率不同,B) 设备有同步与异步开关之分,C) 控制器设备有外置 FET 与集成 FET 之分。图标方式有助于设计师获得符合目标的最优解决方案。

图1:一组在特定输入下方案大小、效率及物料成本之间进行权衡后50种不同的电源解决方案

Footprint 方案大小

BOM Cost 物料清单成本

Efficiency 效率

系统级设计

如果采用此单个电源设计方法并将其应用至整个系统,则可行的设计方法数量就会大幅增加。如图2显示,具有FPGA、内存、通信及马达控制元素的系统板。

图 2:单个系统板中的多重直流负载示例。此示例需要多重电源解决方案。

Power Supply & ProtecTIon 电源与保护

Many loads, Many Supplies 多负载、多电源

Core Supply 核心电源

FPGA IO FPGA IO

Vcca Vcca

Flash

闪存

SDRAM SDRAM

CCD CCD

PLL PLL

Motor Control 马达控制

Miscellaneous 其它

9 Loads and 5 Voltages 9 个负载和 5 种电压

本系统具有48V输入和9个负载。设计系统电源的第一项任务是将电压分组在一起,因此我们共有五种电压。继而,设计师需要确定所需的架构,包括是否需要在源电源与负载点电源之间放置一个或多个中间电压轨。这种情况如图3中所示。

中间电压轨可通过将不同电源的工作周期限制为最佳范围来提高效率,从而提高系统性能。它还可以通过下列方式来减少成本和方案大小:将高压组件限制为中间电源,同时允许下游电源使用低压组件,而低压组件通常价格更便宜且体积更小,尤其是在使用陶瓷电容器时,更是如此。确定电压轨架构后,设计师需要优化电源以减小方案大小、提高效率及/或降低成本。

图3是1个12伏特中间电压轨电源和4个负载点电源组成的典型电源系统架构。上图同时也是每个电源的最优解决方案图表,其中包括大量需要考虑的选项。

采用此方法带来多种可能性。例如,如果有5个不同的电压轨架构和5个不同的电源,而每个电源又有50个可能的电源解决方案,则设计师现在需要考虑1250个选项。再加上5种不同的效率、方案大小和成本优化解决方案,则需要审阅的解决方案总数将增加至6250个。因此,关键是要缩小选择范围,并使用可视化工具来生成符合设计目标的最佳解决方案。图4 显示了通过WEBENCH Power Architect工具生成的不同系统级设计的图表。图表中的每个圆圈面积均代表不同的架构/电压轨配置,以及方案大小、物料成本或效率的不同优化解决方案。正如图中所示,不同解决方案之间的差异非常大。

y 5 (2.5V) 电源 5 (2.5V)

由9个负载电源成系统的25个系统解决方案图表。图中的颜色代表不同的优化解决方案,每个解决方案分别着重于减小系统方案大小、降低系统物料成本或提高系统效率。

优化系统设计

在图4中,不同的颜色代表不同的设计优化解决方案。在为提高效率而优化的设计中,降低了设计的开关频率,以减少交流开关功率损耗并提高系统效率。但是,为了使电感器纹波电流在较低频率下保持不变,特地增加了电感,从而增加了电感器覆盖面积,最终导致整体系统方案变大。同时还导致物料成本增加,而这正是采用较大组件的典型解决方案。

图标右上角的深蓝色表示这些设计。与此相反,在为减小系统方案大小而优化的设计中,则降低了频率,从而允许减小电感与电感器大小,同时使电感器纹波电流保持不变。较小的零件通常会更便宜,整体物料成本也因此而降低。最优解决方案增加了交流开关功率损耗,而降低了效率。这些结果在图表的左下部分以红色表示。图表中所示的其它颜色均为这两个极限值之间的最优解决方案。

显示具有最低物料清单成本、最小组件覆盖面积以及最高效率选项,且由9个负载电源所组成系统的系统解决方案总结。

显示的是电源解决方案数组的极限值,显而易见,我们需要进一步优化设计。要获得91%的最高系统效率,系统物料成本与组件大小将会比其它极限值选项分别高2.8与4.3 倍。与此相反,要获得最低物料成本或最小方案,效率将会降至85%。但设计师也可以选择介于这些极限值之间的选项。因此,我们得出如下结论:凭借可让用户减少并可视化大量多重负载系统级电源解决方案的工具,可以在设计阶段节省大量时间,并根据设计师的特定需求最终获得最优解决方案。

佰维存储2025年上半年实现营业收入3,912,336,913.69元,同比增长13.7%。但受行业周期等因素影响,公司报告期内归属于上市公司股东的净亏损为225,795,502.52元,同比由盈转亏;扣除非经常性损益后的净亏损为231,666,270.28元,同样出现同比下滑。业绩压力主要源于行业价格波动及公司战略性投入增加。

2025年上半年,工业富联(股票代码:601138.SH)实现营业收入3607.6亿元,同比大幅增长35.58%;归属于上市公司股东的净利润达121.13亿元,同比增长38.61%;扣非净利润116.68亿元,同比增长36.73%,核心财务指标均创历史新高。报告期内,公司总资产规模增至3831.28亿元,同比增长20.66%,展现出强劲的资产扩张能力。

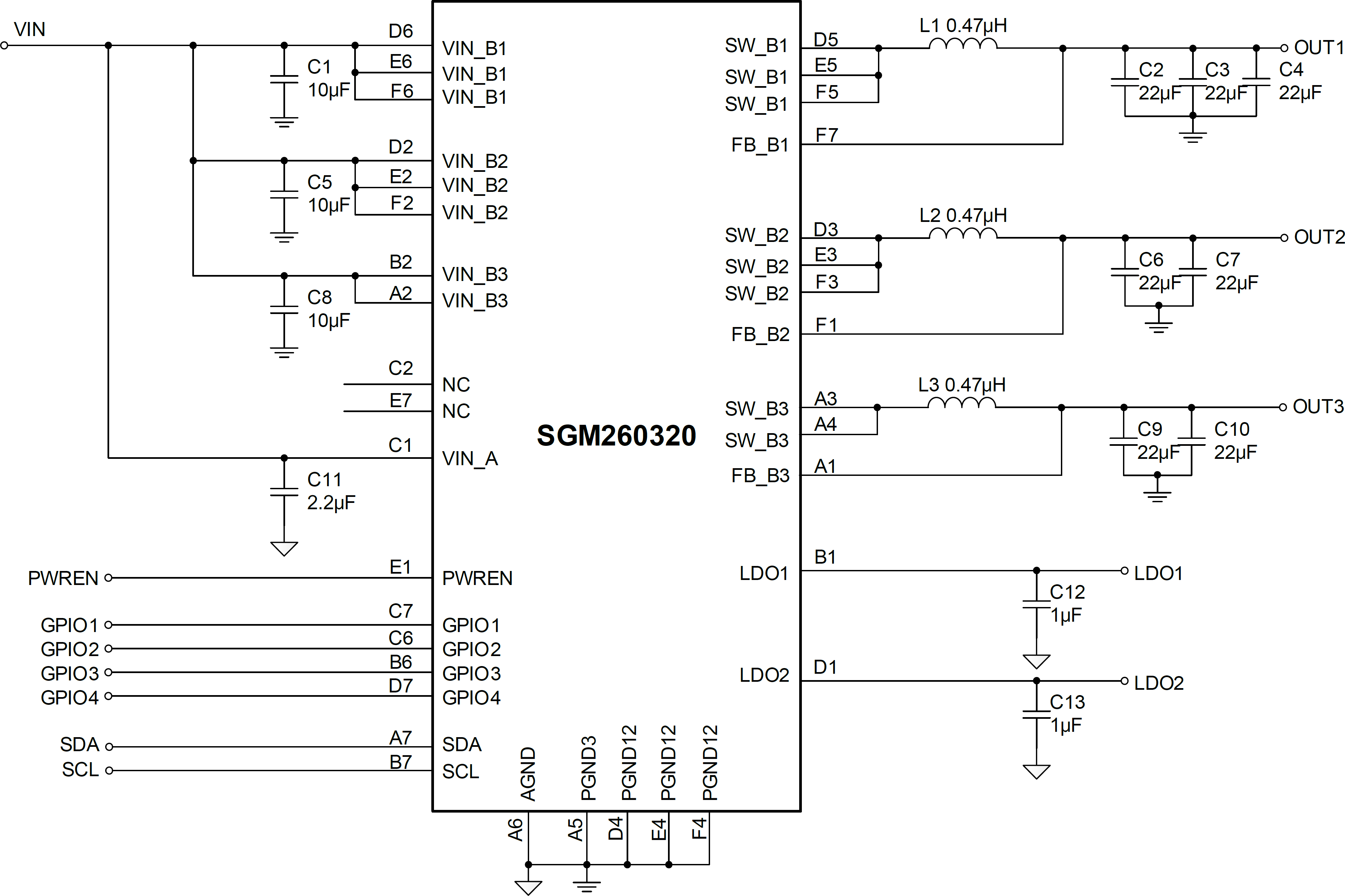

在追求电子设备小型化、高性能和超低功耗的时代,复杂的多轨电源设计已成为研发的关键挑战。传统分立式电源方案不仅占用宝贵的PCB面积,也增加了设计难度与系统功耗控制的复杂性。固态硬盘(SSD)、现场可编程门阵列(FPGA)、微控制器单元(MCU)系统及便携设备对电源管理集成电路(PMIC)的要求日益严苛:高效转换、低待机功耗、高集成度、精确调压以及智能化管理缺一不可。圣邦微电子(SG Micro)推出的SGM260320 PMIC,正是瞄准这一市场需求,以高度集成、卓越性能和丰富的可配置功能,提供了一站式的高效供电解决方案。

随着智能手机影像功能逐渐成为用户核心需求,光学防抖(OIS)技术正面临前所未有的性能挑战。TDK株式会社凭借旗下InvenSense公司15年OIS/EIS技术积累,最新推出的SmartMotion® ICM-536xx系列六轴IMU,正在打破高端防抖技术的成本壁垒。该方案通过突破性的6.4kHz输出数据速率和20位分辨率,首次将专业级防抖性能引入主流移动设备市场。

2024年,全球工业机器人市场经历了一次明显的周期性调整。国际机器人联合会(IFR)的初步统计数据显示,全年新装机量约为52.3万台,较上年下滑约3%。这是近年来该市场罕见出现的负增长,反映出多重经济与技术周期叠加下的复杂局面。