发布时间:2010-08-30 阅读量:2370 来源: 我爱方案网 作者:

中心议题:

解决方案:

随着通信技术的发展,无线射频电路技术运用越来越广,其中的射频电路的性能指标直接影响整个产品的质量,射频电路印制电路板(PCB) 的抗干扰设计对于减小系统电磁信息辐射具有重要的意义。射频电路PCB的密度越来越高,PCB设计的好坏对抗干扰能力影响很大,同一电路,不同的PCB设计结构,其性能指标会相差很大。电磁干扰信号如果处理不当,可能造成整个电路系统的无法正常工作,因此如何防止和抑制电磁干扰,提高电磁兼容性,就成为设计射频电路PCB时的一个非常重要的课题。

电磁兼容性EMC是指电子系统在规定的电磁环境中按照设计要求能正常工作的能力。电子系统所受的电磁干扰不仅来自电场和磁场的辐射,也有线路公共阻抗、导线间耦合和电路结构的影响。在研制设计电路时,希望设计的印制电路板尽可能不易受外界干扰的影响,而且也尽可能小地干扰影响别的电子系统。

设计印制板首要的任务是对电路进行分析,确定关键电路。这就是要识别哪些电路是干扰源,哪些电路是敏感电路,弄清干扰源可能通过什么路径干扰敏感电路。射频电路工作频率高,干扰源主要是通过电磁辐射来干扰敏感电路,因此射频电路PCB板抗干扰设计的目的是减小PCB板的电磁辐射和PCB板上电路之间的串扰。

射频电路板设计

1 元器件的布局

由于SMT一般采用红外炉热流焊来实现元器件的焊接, 因而元器件的布局影响到焊点的质量,进而影响到产品的成品率。而对于射频电路PCB设计而言,电磁兼容性要求每个电路模块尽量不产生电磁辐射,并且具有一定的抗电磁干扰能力,因此元器件的布局也影响到电路本身的干扰及抗干扰能力,直接关系到所设计电路的性能。故在进行射频电路PCB设计时除了要考虑普通 PCB设计时的布局外,主要还须考虑如何减小射频电路中各部分之间的相互干扰、如何减小电路本身对其他电路的干扰以及电路本身的抗干扰能力。

根据经验,射频电路效果的好坏不仅取决于射频电路板本身的性能指标,很大部分还取决于与CPU处理板间的相互影响,因此在进行PCB设计时,合理布局显得尤为重要。布局的总原则是元器件应尽可能同一方向排列,通过选择PCB进入熔锡系统的方向来减少甚至避免焊接不良的现象;根据经验元器件间最少要有 0.5mm的间距才能满足元器件的熔锡要求,若PCB板的空间允许,元器件的间距应尽可能宽。对于双面板一般应设计一面为SMD及SMC元件,另一面则为分立元件。

布局中应注意:

1)首先确定与其他PCB板或系统的接口元器件在PCB板上的位置,必须注意接口元器件间的配合问题(加元器件的方向等);

2)因为掌上用品的体积都很小,元器件间排列很紧凑,因此对于体积较大的元器件,必须优先考虑,确定出相应位置,并考虑相互间的配合问题;

3)认真分析电路结构,对电路进行分块处理(加高频放大电路、混频电路及解调电路等),尽可能将强电信号和弱电信号分开,将数字信号电路和模拟信号电路分开,完成同一功能的电路应尽量安排在一定的范围之内,从而减小信号环路面积;各部分电路的滤波网络必须就近连接,这样不仅可以减小辐射,而且可以减少被干扰的机率,提高电路的抗干扰能力;

4)根据单元电路在使用中对电磁兼容性敏感程度不同进行分组。对于电路中易受干扰部分的元器件在布局时还应尽量避开干扰源(比如来自数据处理板上CPU的干扰等)。

2 布 线

在基本完成元器件的布局后,就可开始布线了。布线的基本原则为:在组装密度许可情况下,尽量选用低密度布线设计,并且信号走线尽量粗细一致,有利于阻抗匹配。

对于射频电路,信号线的走向、宽度、线间距的不合理设计,可能造成信号传输线之间的交叉干扰;另外,系统电源自身还存在噪声干扰,所以在设计时频电路 PCB时一定要综合考虑,合理布线。布线时,所有走线应远离PCB板的边框2mm左右,以免PCB板制作时造成断线或有断线的隐患。

电源线要尽可能宽,以减少环路电阻,同时使电源线、地线的走向和数据传递的方向一致,以提高抗干扰能力;所布信号线应尽可能短,并尽量减少过孔数目;各元器件间的连线越短越好,以减少分布参数和相互间的电磁干扰;对不相容的信号线应尽量相互远离,且尽量避免平行走线,而在正反两面的信号线应相互垂直;布线时在需要拐角的地方应以135°角为宜,避免拐直角。

布线时与焊盘直接相连的线条不宜太宽,走线应尽量离开不相连的元器件,以免短路;过孔不宜画在元器件上,且应尽量远离不相连的元器件,以免在生产中出现虚焊、连焊、短路等现象。在射频电路PCB设计中,电源线和地线的正确布线显得尤其重要,合理的设计是克服电磁干扰的最重要的手段。

PCB上相当多的干扰源是通过电源和地线产生的,其中地线引起的噪声干扰最大。地线容易形成电磁干扰的主要原因在于地线存在阻抗。当有电流流过地线时,就会在地线上产生电压,从而产生地线环路电流,形成地线的环路干扰。当多个电路共用一段地线时,就会形成公共阻抗耦合,从而产生所谓的地线噪声。

因此,在对射频电路PCB的地线进行布线时应该做到:

1)对电路进行分块处理时,射频电路基本上可分成高频放大、混频、解调、本振等部分,要为各个电路模块提供一个公共电位参考点,即各模块电路各自的地线, 这样信号就可以在不同的电路模块之间传输。然后,汇总于射频电路PCB接入地线的地方,即汇总于总地线。由于只存在一个参考点,因此没有公共阻抗耦合存在,从而也就没有相互干扰问题;

2)数字区与模拟区尽可能以地线进行隔离,并且数字地与模拟地要分离,最后接于电源地;

3)在各部分电路内部的地线也要注意单点接地原则,尽量减小信号环路面积,并与相应的滤波电路的地线就近相接;

4)在空间允许的情况下,各模块之间最好能以地线进行隔离,防止相互之间的信号耦合效应。

[page]

实验测试

下面几个实验测试事例,说明了不同原因带来的干扰及其实际的解决办法。

1 电源线和地线带来的干扰

图1取自某高压控制保护PCB的部分电路。图1a为原设计电路。由于电源线和地线的印制导线宽度太细,电路在工作时局受外界干扰;图1b是经过改进后的电路,其电源线和地线加粗至5mm,解决了电路的干扰问题。

图1 某高压控制保护PCB的部分电路

2 元器件布局不合理带来的干扰

图2取自某雷达发射机磁场控制保护PCB的部分电路。重新布局元器件后改进的PCB电路(如图2b)较改进前的PCB电路(如图2a)在抗干扰性能上有很大的改善。

图2 某雷达发射机磁场控制保护PCB的部分电路

3 布线不合理带来的干扰

图3取自某雷达CFA电源控制保护PCB的部分电路。图3a为原设计电路。由于布线时将高压取样信号线布于闭环取样回路中,使闭环取样电路在工作时易受外界的干扰,造成经常误报过压故障;而图3b是经过改进后的PCB电路,由于避开了高压取样信号线带来的干扰,改进后的PCB电路工作可靠稳定。

图3 某雷达CFA电源控制保护PCB的部分电路

射频电路PCB设计的关键在于如何减少辐射能力以及如何提高抗干扰能力,合理的布局与布线是设计时频电路PCB的保证。文中所述方法有利于提高射频电路PCB设计的可靠性,解决好电磁干扰问题,进而达到电磁兼容的目的。

全球领先的传感器与功率IC解决方案供应商Allegro MicroSystems(纳斯达克:ALGM)于7月31日披露截至2025年6月27日的2025财年第一季度财务报告。数据显示,公司当季实现营业收入2.03亿美元,较去年同期大幅提升22%,创下历史同期新高。业绩增长主要源于电动汽车和工业两大核心板块的强劲需求,其中电动汽车相关产品销售额同比增长31%,工业及其他领域增速高达50%。

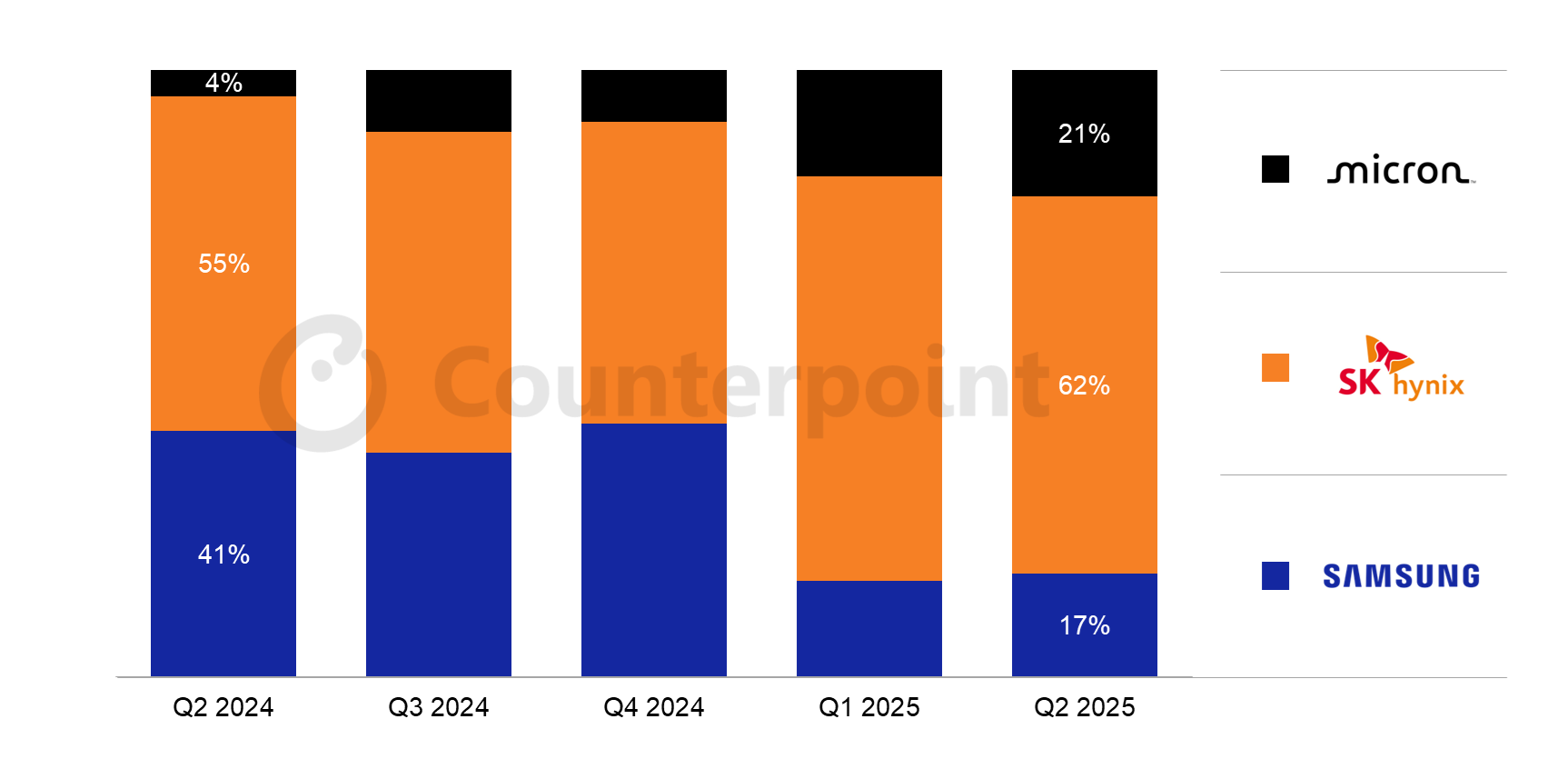

受强劲的人工智能(AI)需求驱动,全球存储芯片市场格局在2025年第二季度迎来历史性转折。韩国SK海力士凭借在高带宽存储器(HBM)领域的领先优势,首次超越三星电子,以21.8万亿韩元的存储业务营收问鼎全球最大存储器制造商。三星同期存储业务营收为21.2万亿韩元,同比下滑3%,退居次席。

8月1日,英伟达官网更新其800V高压直流(HVDC)电源架构关键合作伙伴名录,中国氮化镓(GaN)技术领军企业英诺赛科(Innoscience)赫然在列。英诺赛科将为英伟达革命性的Kyber机架系统提供全链路氮化镓电源解决方案,成为该名单中唯一入选的中国本土供应商。此重大突破性合作直接推动英诺赛科港股股价在消息公布当日一度飙升近64%,市场反响热烈。

全球领先的功率半导体解决方案供应商MPS(Monolithic Power Systems)于7月31日正式公布截至2025年6月30日的第二季度财务报告。数据显示,公司本季度业绩表现亮眼,多项核心指标实现显著增长,并释放出持续向好的发展信号。

贸泽电子(Mouser Electronics)于2025年8月正式推出工业自动化资源中心,为工程技术人员提供前沿技术洞察与解决方案库。该平台整合了控制系统、机器人技术及自动化软件的最新进展,旨在推动制造业向智能化、可持续化方向转型。